### АО "МЦСТ"

На правах рукописи

### Гимпельсон Вадим Дмитриевич

# Сокращение длины критических путей при динамической трансляции двоичных кодов

05.13.11 - "Математическое и программное обеспечение вычислительных машин, комплексов и компьютерных сетей"

Диссертация на соискание учёной степени кандидата физико-математических наук

Научный руководитель

к.т.н. Волконский Владимир Юрьевич

### Содержание:

| СОДЕРЖАНИЕ:                                                                         | 2  |

|-------------------------------------------------------------------------------------|----|

| ВВЕДЕНИЕ                                                                            | 5  |

| Актуальность работы                                                                 | 5  |

| Цель исследования                                                                   | 8  |

| Научная новизна                                                                     | 9  |

| Результаты работы, выносимые на защиту                                              | 9  |

| Теоретическая и практическая значимость.                                            | 10 |

| Апробация                                                                           | 10 |

| Публикации                                                                          | 11 |

| Личный вклад автора                                                                 | 11 |

| Структура и объём работы.                                                           | 11 |

| 1. ДВОИЧНАЯ ТРАНСЛЯЦИЯ И МЕТОДЫ СОКРАЩЕНИЯ ДЛИНЫ                                    |    |

| КРИТИЧЕСКОГО ПУТИ В ГРАФЕ ЗАВИСИМОСТЕЙ                                              | 12 |

| 1.1. Двоичная трансляция                                                            | 12 |

| 1.2. Обзор основных особенностей ЕРІС архитектур                                    | 18 |

| 1.3. Обзор внутреннего представления в компиляторе                                  | 21 |

| 1.3.1. Внутреннее представление                                                     | 21 |

| 1.3.2. Граф зависимостей                                                            | 25 |

| 1.3.3. Особенности графа зависимостей в динамическом двоичном трансляторе           | 27 |

| 1.4. Ускорение результирующего кода за счёт сокращения длины критических путей      | 31 |

| 1.4.1. Ациклические области                                                         | 31 |

| 1.4.1.1. Классические оптимизации с точки зрения сокращения длины критических путей | 31 |

| 1.4.1.2. Специализированные преобразования для сокращении длины критических путей   |    |

| 1.4.2. Циклические области                                                          |    |

| 1.4.2.1. Основные идеи конвейеризации циклов                                        |    |

| 1.4.2.2. Аппаратная поддержка конвейеризации циклов                                 |    |

| 1.6. Выводы                                                                         |    |

|                                                                                     | 40 |

| 2. СОКРАЩЕНИЕ ДЛИНЫ КРИТИЧЕСКИХ ПУТЕЙ В АЦИКЛИЧЕСКИХ                                |    |

| ОБЛАСТЯХ БЕЗ ПОСТРОЕНИЯ НОВЫХ ОПЕРАЦИЙ                                              | 41 |

| 2.1. МЕТОДЫ РАЗРЫВА ЗАВИСИМОСТЕЙ БЕЗ ПОСТРОЕНИЯ НОВЫХ ОПЕРАЦИЙ                      | 41 |

| 2.2. Обзор существующих методов минимизации высоты графа зависимостей               | 43 |

| 2.2.1. Переименование регистров                                                     | 43 |

| 2.2.2. Использование частичных предикатов                                           |    |

| 2.3. Схема работы двоичного транслятора для архитектуры "Эльбрус"                   | 44 |

| 2.4. Минимизация высоты графа зависимостей без построения новых операций            |    |

| 2.4.1. Переименование регистров                                                     | 45 |

| 2.4.2. Спекулятивность по управлению                                                | 50 |

|             | 2.4.3. | Частичные предикаты                                                    | 51  |

|-------------|--------|------------------------------------------------------------------------|-----|

|             | 2.4.4. | Схема работы двоичного компилятора с учётом алгоритмов минимизации без |     |

|             |        | построения новых операций                                              | 60  |

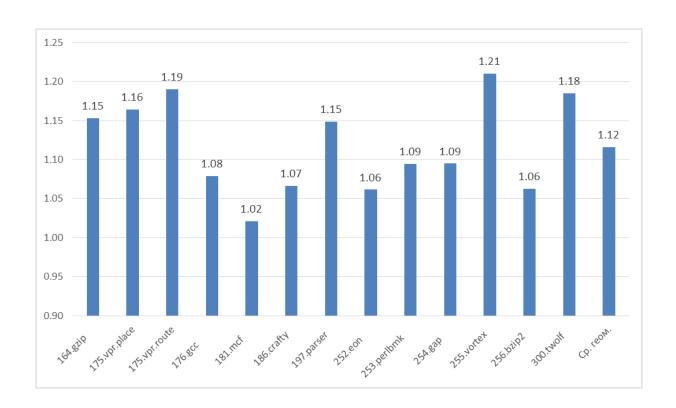

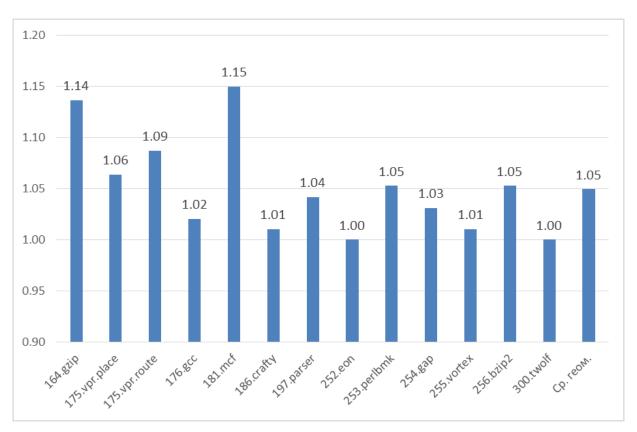

| 2.5.        | Экс    | ПЕРИМЕНТАЛЬНЫЕ РЕЗУЛЬТАТЫ                                              | 61  |

| 2.6.        | Вы     | воды                                                                   | 64  |

| <b>3.</b> C | 'OKDA  | ЩЕНИЕ ДЛИНЫ КРИТИЧЕСКИХ ПУТЕЙ В АЦИКЛИЧЕСКИХ                           |     |

|             |        | X С ПОСТРОЕНИЕМ НОВЫХ ОПЕРАЦИЙ                                         | 66  |

| 3.1.        | ME     | ГОДЫ РАЗРЫВА ЗАВИСИМОСТЕЙ С ПОМОЩЬЮ ПОСТРОЕНИЯ НОВЫХ ОПЕРАЦИЙ          | 66  |

| 3.2.        | ОБЗ    | ОР СУЩЕСТВУЮЩИХ АЛГОРИТМОВ МИНИМИЗАЦИИ ВЫСОТЫ ГРАФА ЗАВИСИМОСТЕЙ       | 75  |

|             | 3.2.1. | Разрыв зависимостей и минимизация высоты графа зависимостей в          |     |

|             |        | суперблоках                                                            | 75  |

|             | 3.2.2. | Минимизация высоты графа зависимостей в процессе работы планировщика   | 76  |

|             | 3.2.3. | Минимизация высоты графа зависимостей в гиперблоках                    | 77  |

|             | 3.2.4. | Минимизация высоты графа зависимостей с помощью решения задачи         |     |

|             |        | целочисленного линейного программирования                              | 78  |

|             | 3.2.5. | Проблемы и недостатки существующих методов минимизации высоты графа    |     |

|             |        | зависимостей                                                           | 79  |

| 3.3.        | Оы     | ЦЕЕ ОПИСАНИЕ АЛГОРИТМА МИНИМИЗАЦИИ ВЫСОТЫ ГРАФА ЗАВИСИМОСТЕЙ           |     |

|             | OCH    | ЮВАННОГО НА ТЕХНИКАХ РАЗРЫВА С ПОСТРОЕНИЕМ НОВЫХ ОПЕРАЦИЙ              | 83  |

|             | 3.3.1. | Вводные замечания                                                      | 83  |

|             | 3.3.2. | Формализация задачи                                                    | 85  |

|             | 3.3.3. | Формальное описание алгоритма минимизации высоты графа зависимостей    | 86  |

|             | 3.3.4. | Доказательство корректности алгоритма                                  | 91  |

|             | 3.3.5. | Оптимальность алгоритма                                                | 91  |

|             | 3.3.6. | Оценка сложности алгоритма                                             |     |

| 3.4.        | Изв    | АВЛЕНИЕ ОТ ИЗЛИШНЕЙ СПЕКУЛЯТИВНОСТИ ДЛЯ ОПЕРАЦИЙ ЧТЕНИЯ ИЗ ПАМЯТИ      | 96  |

| 3.5.        | CXE    | ЕМА РАБОТЫ ДВОИЧНОГО ОПТИМИЗИРУЮЩЕГО ТРАНСЛЯТОРА С УЧЁТОМ АЛГОРИТМОВ   |     |

|             | МИН    | НИМИЗАЦИИ ВЫСОТЫ ГРАФА ЗАВИСИМОСТЕЙ                                    | 99  |

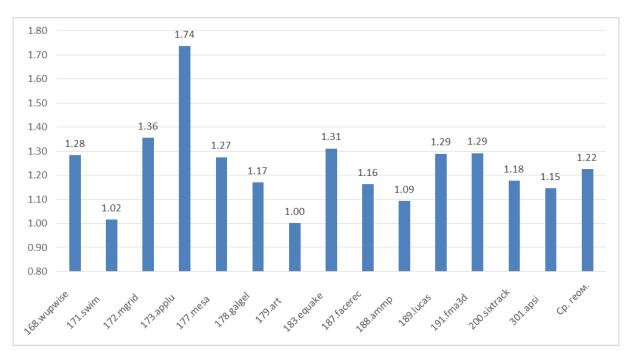

| 3.6.        | Экс    | ПЕРИМЕНТАЛЬНЫЕ РЕЗУЛЬТАТЫ                                              | 100 |

| 3.7.        | Вы     | зоды                                                                   | 103 |

| <b>4.</b> C | СОКРА  | .ЩЕНИЕ ДЛИНЫ КРИТИЧЕСКИХ ПУТЕЙ В ЦИКЛИЧЕСКИХ ОБЛАСТЯХ                  | 105 |

| 4.1.        | ОБЗ    | ОР СУЩЕСТВУЮЩИХ АЛГОРИТМОВ КОНВЕЙЕРИЗАЦИИ ЦИКЛОВ                       | 105 |

|             | 4.1.1. | Основные определения                                                   | 105 |

|             | 4.1.2. | Модульное планирование.                                                | 106 |

|             | 4.1.3. | URCR, URPR, GURPR u GURPR*                                             | 108 |

|             | 4.1.4. | Enhanced Pipeline Scheduling                                           | 109 |

|             | 4.1.5. | Другие алгоритмы конвейеризации                                        | 110 |

|             | 4.1.6. | Проблемы и недостатки существующих методов конвейеризации циклов       | 111 |

| 4.2.        | PAC    | ШИРЕННЫЙ ГРАФ ЗАВИСИМОСТЕЙ                                             | 112 |

|             | 4.2.1. | Расширение графа зависимостей                                          | 112 |

| 13          | Пол    | ІСИЁТ МИНИМА ПЬНОГО ВАЗМЕВА ВЫСОТЫ ШИК ПА                              | 11/ |

|        | 4.3.1.       | Ограничения снизу на размер физической итерации цикла                      | . 114 |

|--------|--------------|----------------------------------------------------------------------------|-------|

|        | 4.3.2.       | Подсчёт ограничения по ресурсам                                            | . 115 |

|        | 4.3.3.       | Подсчёт максимальной длины рекуррентности                                  | . 116 |

| 4.4    | . PA3        | ВМЕТКА ВРЕМЁН РАННЕГО И ПОЗДНЕГО ПЛАНИРОВАНИЯ НА РАСШИРЕННОМ ГРАФЕ         |       |

|        | 3AB          | ИСИМОСТЕЙ                                                                  | . 120 |

|        | 4.4.1.       | Времена раннего и позднего планирования на расширенном графе зависимостей  | . 120 |

|        | 4.4.2.       | Алгоритм разметки времён планирования на расширенном графе зависимостей    | . 121 |

|        | 4.4.3.       | Корректность и оптимальность алгоритма                                     | . 126 |

| 4.5    | Алі          | ГОРИТМ КОНВЕЙЕРИЗАЦИИ ЦИКЛОВ.                                              | . 128 |

|        | 4.5.1.       | Описание алгоритма конвейеризации циклов                                   | . 128 |

|        | 4.5.2.       | Разрыв зависимостей в процессе работы алгоритма конвейеризации циклов      | . 130 |

|        | 4.5.3.       | Оценка сложности алгоритма конвейеризации                                  | . 130 |

|        | 4.5.         | 3.1. Оценка сложности алгоритма разметки времён планирования               | 131   |

|        | 4.5.         | 3.2. Оценка сложности алгоритма конвейеризации циклов                      | 135   |

| 4.6    | <b>5.</b> Ап | ПАРАТНАЯ ПОДДЕРЖКА ОБЕСПЕЧЕНИЯ ТОЧНОГО КОНТЕКСТА ПРИ ИСПОЛЬЗОВАНИИ         |       |

|        | BPA          | ЩАЮЩИХСЯ РЕГИСТРОВ                                                         | . 136 |

|        | 4.6.1.       | Обеспечение точного контекста                                              | . 136 |

|        | 4.6.2.       | Взаимодействие схемы восстановления точного контекста с механизмом         |       |

|        |              | вращающихся регистров                                                      | . 137 |

| 4.7    | . Hei        | КОТОРЫЕ ОБОБЩЕНИЯ                                                          | . 139 |

|        | 4.7.1.       | Использование конвейеризации для циклов с несколькими обратными дугами     |       |

|        | 4.7.2.       | Использование конвейеризации для внешних циклов                            | . 140 |

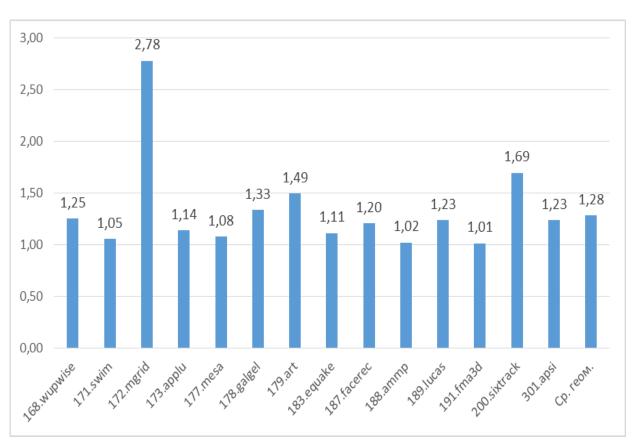

| 4.8    | 3. Эко       | СПЕРИМЕНТАЛЬНЫЕ РЕЗУЛЬТАТЫ                                                 | . 142 |

| 4.9    | . Вы         | воды                                                                       | . 144 |

| ЗАК.   | ЛЮЧЕ         | СНИЕ.                                                                      | . 145 |

| СПП    | COL          | HITEDATVDI I                                                               | 1.40  |

|        |              |                                                                            | . 148 |

|        |              | ЛЬСТВА О ГОСУДАРСТВЕННОЙ РЕГИСТРАЦИИ ПРОГРАММЫ ДЛЯ                         |       |

| ЭВМ    | [            |                                                                            | . 157 |

| СПИ    | ІСОК І       | ИЛЛЮСТРАЦИЙ                                                                | . 158 |

| СПИ    | ІСОК Т       | ГАБЛИЦ                                                                     | . 160 |

| ПРИ    | ЛОЖІ         | ЕНИЕ А. ОПИСАНИЕ АЛГОРИТМА КОНВЕЙЕРИЗАЦИИ ЦИКЛОВ                           |       |

|        |              | PIPELINING                                                                 | . 161 |

|        |              | ЕНИЕ Б. ОПИСАНИЕ АЛГОРИТМА КОНВЕЙЕРИЗАЦИИ ЦИКЛОВ С                         |       |

|        |              | СНИЕ Б. ОПИСАНИЕ АЛІ ОРИТМА КОНВЕИЕРИЗАЦИИ ЦИКЛОВ С<br>ОВАНИЕМ СЕТЕЙ ПЕТРИ | 164   |

| ri Cli | widi         | UDAHMEN QETEN HETEN                                                        | . 104 |

### Введение.

### Актуальность работы.

Повышение производительности является одним из главных направлений развития вычислительной техники в течение всей её истории. Во многих отраслях производительность является основным требованием, предъявляемым к вычислительным комплексам. Инвестируются огромные средства в развитие новых архитектур микропроцессоров и вычислительных комплексов.

Одним из подходов к увеличению производительности микропроцессоров является логическое усовершенствование внутренней архитектуры, позволяющее извлекать параллелизм на уровне отдельных операций. Есть разные способы извлечения параллелизма между операциями.

Одним из первых подходов к созданию микропроцессорных архитектур, извлекающих параллелизм на уровне отдельных операций, является так называемая суперскалярная архитектура. В таких микропроцессорах независимость между отдельными операциями (а именно это свойство позволяет распараллеливать код) определяется на аппаратном уровне. Это даёт возможность при неизменной системе команд микропроцессора создавать всё более и более производительные решения за счёт улучшения микроархитектуры конвейера. Однако недостатком суперскалярной существенным архитектуры является TO, реализованный на аппаратном уровне, является динамическим по своей природе и, следовательно, имеет серьёзные ограничения из-за своей сложности. Это приводит к невозможности проанализировать большое количество операций одновременно, так как усложнения различных анализов влекут за собой нелинейный рост необходимого оборудования и увеличение выделяемой энергии.

Одним из путей устранения описанных ограничений суперскалярной архитектуры является разработка микропроцессорных архитектур с явно выраженной параллельностью на уровне команд. Такие архитектуры в середине 90-х годов получили название *EPIC* (*Explicitly Parallel Instruction Computing*) [14], [15]. Особенностью таких архитектур является то, что практически вся работа по распараллеливанию на уровне операций перекладывается с аппаратуры на компилятор, а в результирующем коде параллельность между операциями выражается явно. Такой подход избавляет от необходимости аппаратной реализации распараллеливания операций, что позволяет увеличить параллелизм по сравнению с суперскалярными архитектурами.

При разработке новых микропроцессорных архитектур часто приходиться сталкиваться с серьёзным недостатком, препятствующим их быстрому массовому распространению — это

новая несовместимая система команд. Для существующих архитектур создано и отлажено огромное количество программного обеспечения. Это программное обеспечение в лучшем случае придётся перекомпилировать для перехода на новую архитектуру, а в худшем придётся разрабатывать заново, так как исходные тексты программ могут быть не доступны.

Многие разработчики микропроцессоров использовали и продолжают использовать аппаратный метод обеспечения двоичной совместимости со старыми архитектурами [16], [17]. Однако такой подход не всегда достаточно эффективен, так как разработчики вынуждены поддерживать многие свойства ранее разработанных архитектур, и следовательно наследуются недостатки этих архитектур, что приводит к снижению итоговой производительности.

Существует альтернативный способ обеспечения двоичной совместимости, получивший название *двоичной трансляции*. Суть этого метода заключается в программной перекомпиляции (перетрансляции) двоичных кодов платформы, с которой мы хотим обеспечить совместимость (исходная архитектура), в коды новой платформы (целевая архитектура). Достоинствами этого подхода являются высокая эффективность и возможность его применения для широкого класса исходных и целевых архитектур.

Важной особенностью двоичного транслятора является то, что он должен быть динамическим, то есть трансляция (компиляция) кода исходного приложения происходит во время его исполнения. Это связано с тем, что практически любая микропроцессорная архитектура позволяет создавать код динамически и затем исполнять его. Таким образом, время работы приложения под управлением двоичного транслятора складывается из времени работы оттранслированных кодов и времени, затраченным на трансляцию этих кодов. В силу этого на скорость трансляции должны быть наложены очень жёсткие ограничения. С другой стороны для получения быстрого результирующего кода необходимо проводить различные оптимизации, часто тяжеловесные. Как же совместить эти два условия для получения эффективной системы двоичной трансляции?

Хорошо известно, что в большинстве программ код используется неравномерно [49]. Большая часть времени работы проводится в коде, занимающем очень небольшую часть программы. Таким образом, чтобы двоичный транслятор мог обеспечить общую высокую эффективность, сравнимую с кодами, полученными из-под языкового компилятора, он должен включать в себя несколько уровней трансляторов (оптимизирующих компиляторов), различающихся между собой качеством и количеством проводимых оптимизаций кода, а также временем работы. Выбор, каким транслятором оптимизировать данный код, производится на основе профильной информации, которая собирается в процессе работы исходной программы. Чем дольше код работает, тем полезнее будет оттранслировать этот код транслятором, дающим более быстрый код целевой архитектуры. Транслятор верхнего уровня (дающий самый

быстрый код целевой архитектуры), будем далее называть двоичным оптимизирующим транслятором.

Двоичный оптимизирующий транслятор с целевой ЕРІС архитектурой для получения быстрого результирующего кода должен уметь производить оптимизации специфичные для архитектур: построение предикатного ЭТИХ конвейеризация циклов, сокращение критического пути и т.д. Без такого минимального набора оптимизаций невозможно достичь высокой производительности результирующих кодов. В тоже время условия, в которых работает двоичный оптимизирующий транслятор, накладывают серьёзные ограничения и выдвигают определённые требования к алгоритмам, используемым в двоичном оптимизирующем трансляторе. Во-первых, это дополнительные семантические свойства, накладываемые особой спецификой двоичной трансляции. Пожалуй, основным семантическим ограничением является задача обеспечения точного состояния регистров и памяти исходной архитектуры при возникновении прерываний и исключений. Вторым важным требованием, предъявляемым к алгоритмам оптимизаций, является уже упомянутая выше, собственная скорость работы этих алгоритмов.

Одними ИЗ важнейших оптимизаций для архитектур с явно выраженной параллельностью являются оптимизации позволяющие сократить время исполнения за счёт распараллеливания вычислений. Одними ИЗ эффективных методов позволяющих распараллелить вычисления являются оптимизации производящие сокращение критического пути (или просто сокращение критического пути) в ациклических областях. Критическим путём называют последовательность связанных (зависимых) операций, таких, что длина вычислений этой последовательности максимальна в данном блоке. Соответственно длина критического пути определяет длину вычислений всего блока, и сократив критический путь мы ускорим вычисления. В рассматриваемых архитектурах имеется большое количество исполняющих устройств, поэтому часто оказывается, что сокращение критического пути за счёт построения одной или нескольких новых операций даёт ускорение результирующего кода.

Отдельно необходимо отметить техники по уменьшению времени выполнения циклов. Здесь применим класс оптимизаций, который получил название "конвейеризация циклов методом наложения итераций" или, в англоязычной литературе, "программная конвейеризация циклов" (software pipelining). Суть этого класса оптимизаций заключается в том, что возможно совместить вычисление нескольких итераций цикла в одной итерации цикла результирующего кода. В совокупности с методами сокращения критического пути в ациклических областях, специализированные методы интегрирующие конвейеризацию циклов с сокращением критических путей, позволяют получить более быстрый результирующий код.

Необходимость создания быстрых алгоритмов сокращения критического пути и конвейеризации циклов в двоичном оптимизирующем трансляторе, позволяющих максимально использовать возможности архитектуры с явным выраженной параллельностью на уровне команд, и как следствие, достижение эффективной совместимости, определяет актуальность диссертационной работы.

#### Цель исследования.

Целью диссертационной работы является повышение эффективности двоичного оптимизирующего транслятора за счёт адаптации старых и разработки новых алгоритмов сокращения длины критического пути в циклических и ациклических областях для архитектур с явно выраженной параллельностью на уровне команд. Эти алгоритмы должны учитывать особенности оптимизирующего двоичного транслятора: специфическое окружение и требования скорости работы. В соответствии с этими целями были определены следующие задачи:

- провести анализ современного уровня развития методов сокращения длины критического пути в циклических и ациклических областях, и возможностей их использования в двоичном оптимизирующем трансляторе;

- разработка новых алгоритмов сокращения длины критического пути в ациклических областях;

- разработка новых алгоритмов сокращения длины критического пути в циклических областях основанных на конвейеризации циклов;

- интеграция методов сокращения длины критического пути в ациклических областях с алгоритмом конвейеризации циклов;

- разработка метода интеграции алгоритма сокращения длины критического пути с другими оптимизирующими преобразованиями с целью устранения ситуаций, когда качество некоторой оптимизации зависит от результатов работы алгоритма сокращения длины критического пути, а качество алгоритма сокращения длины критического пути зависит от этой оптимизации;

- обеспечение во всех разрабатываемых алгоритмах семантических требований, накладываемых двоичной трансляцией, и высокой скорости работы всех разрабатываемых алгоритмов;

- реализация указанных алгоритмов в динамическом двоичном трансляторе.

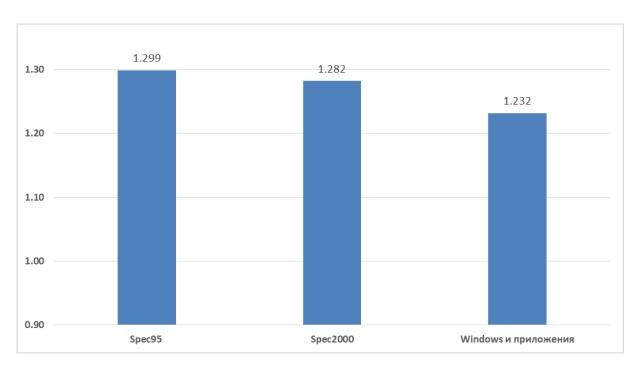

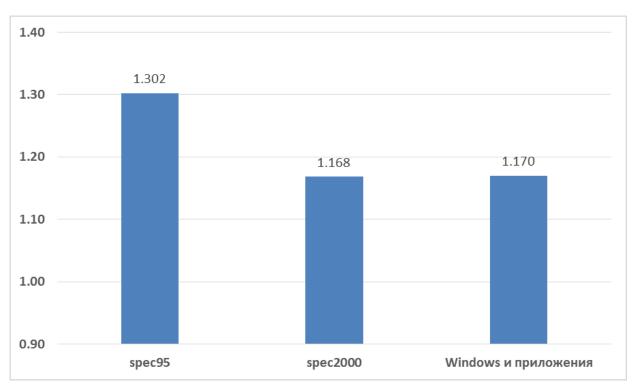

**Методы исследования** заимствованы из областей системного программирования, технологии компиляции, теории графов, теории алгоритмов. Эффективность предложенных

методов оценивалась путём замера ключевых параметров предлагаемых алгоритмов, а также замеров времени исполнения задач на вычислительном комплексе с микропроцессором "Эльбрус" и на потактной модели микропроцессора Эльбрус-S. Замеры производились на пакетах задач SPEC CPU95 [71] и SPEC CPU2000 [72]. Также для анализа качества результирующего кода использовались горячие участки операционной системы Windows 2000 и горячие участки типичных пользовательских приложений для этой ОС: Microsoft Word, Microsoft Power Point, Internet Explorer и многие другие.

### Научная новизна.

Научной новизной обладают следующие результаты работы:

- быстрый алгоритм сокращения длины критического пути в ациклических областях;

- схема взаимодействия алгоритма сокращения длины критического пути в ациклических областях с другими оптимизирующими преобразованиями для преодоления "замкнутого круга", когда оптимизации являются взаимозависимыми;

- алгоритм разметки времён раннего и позднего планирования на расширенном графе зависимостей;

- алгоритм конвейеризации циклов в динамическом двоичном оптимизирующем трансляторе;

- интеграция алгоритмов сокращения длины критического пути с алгоритмом конвейеризации циклов;

- сформулированы и доказаны теоремы, показывающие корректность и оптимальность предложенных алгоритмов, а также произведена оценка сложности этих алгоритмов.

### Результаты работы, выносимые на защиту.

В процессе проведения диссертационного исследования были получены следующие результаты, выносимые на защиту:

- разработка и реализация быстрого алгоритма сокращения длины критического пути в ациклических областях; теорема об оптимальности предложенного алгоритма;

- алгоритм разметки времён раннего и позднего планирования на расширенном графе зависимостей; сформулированы и доказаны теоремы о корректности, оптимальности и сложности предложенного алгоритма;

- алгоритм конвейеризации циклов в динамическом двоичном оптимизирующем трансляторе; сформулирована и доказана теорема о сложности предложенного алгоритма; интеграция методов сокращения длины критического пути в ациклических областях с алгоритмом конвейеризации циклов.

### Теоретическая и практическая значимость.

Предложен алгоритм сокращения длинны критического пути в ациклических областях. Предложен алгоритм разметки времён на расширенном графе зависимостей и основе него разработан алгоритм конвейеризации циклов.

Практическая ценность диссертационной работы состоит в том, что на основе предложенных алгоритмов удалось значительно повысить эффективность работы динамического двоичного транслятора для архитектуры "Эльбрус". Впервые было показано, что аппаратная техника вращающихся регистров может эффективно применяться в двоичном трансляторе. Результаты исследований были реализованы в следующих программных и аппаратных системах:

- динамический двоичный оптимизирующий транслятор уровня всей системы с архитектуры Intel x86 на архитектуру "Эльбрус", разработанный в АО "МЦСТ";

- динамический двоичный оптимизирующий транслятор уровня приложений ОС Linux с архитектуры Intel x86 на архитектуру "Эльбрус", разработанный в АО "МЦСТ";

- статический оптимизирующий транслятор с архитектуры Intel x86 на архитектуру IPF (Itanium), разработанный в АО "МЦСТ" в рамках совместного проекта с Intel Corporation;

- микропроцессор Эльбрус, разработанный в АО "МЦСТ", обеспечивающий совместимость с архитектурой Intel x86;

- динамический двоичный транслятор уровня приложений ОС Linux, разработанный в ООО "Эльбрус Технологии".

Предложенные алгоритмы также могут быть использованы в оптимизирующих компиляторах и двоичных трансляторах для различных архитектур.

#### Апробация.

Основные результаты диссертационной работы докладывались на следующих научнотехнических конференциях и семинарах:

- 5th RISC-V Workshop, Mountain View, CA, November 29-30, 2016.

- Open Conference on Compiler Technologies, Москва, РАН, 2015 г.

- Samsung Compiler Workshop, Mockba, Samsung Office, 2014 г.

- На XXXIV Международной молодёжной научной конференции "Гагаринские чтения", Москва, МАТИ, 2008 г.

- Международная научная конференция, посвящённая 80-летию со дня рождения академика В.А. Мельникова, 2008 г.

- На XXIII научно-технической конференции "Направления развития и применения перспективных вычислительных средств и новый информационных технологий в ВВТ РКО", Москва, в/ч 03425, 2007 г.

- На XXXIII Международной молодёжной научной конференции "Гагаринские чтения", Москва, МАТИ, 2007 г.

- На XXI научно-технической конференции войсковой части 03425. Москва, в/ч 03425, 2003 г.

- На семинарах секции программного обеспечения ЗАО "МЦСТ" в 2005-2016 годах.

### Публикации.

По теме диссертации опубликовано 13 печатных работ [1]-[13]. Работы [3], [4], [7], [10], [12] опубликованы в изданиях из перечня ВАК. В работе [12] описаны методы сокращения длины критических путей в ациклических областях. Личный вклад автора заключается в разработке и реализации быстрого алгоритма минимизации высоты графа зависимостей. В работах [4] и [8] представлены методы сокращения длины критических путей в циклах. В работах [1] и [2] личный вклад автора заключается в переносе алгоритмов, изложенных в данной диссертационной работе, в динамические двоичные трансляторы из x86 в ARM и из RISC-V в x86. Работа [3] написана совместно с несколькими авторами. Личный вклад автора в этой работе заключается в описании общей схемы функционирования динамического двоичного транслятора, а также описания оптимизирующего двоичного транслятора, из х86 в "Эльбрус". В работе [7] личный вклад автора заключается в постановке задачи и в разработке методов коррекции профильной информации в случае её не консистентности. В работе [10] личный вклад автора заключается в предложенных методах активации оптимизаций в двоичном трансляторе. Совместная работа [13] посвящена методам обеспечения точного состояния контекста в двоичном трансляторе. Личный вклад автора заключается в реализации и поддержке этих методов в алгоритмах сокращения длины критического пути.

В ходе выполнения работы было получено свидетельство о государственной регистрации программ для ЭВМ [1, см. стр. 157].

#### Личный вклад автора.

Все представленные в диссертации результаты получены лично автором.

### Структура и объём работы.

Работа состоит из введения, четырёх глав, заключения и двух приложений. Основной текст диссертации (без приложений и списка литературы) занимает 147 страницы, общий объем – 166 страниц. Список литературы содержит 113 наименований.

### 1. Двоичная трансляция и методы сокращения длины критического пути в графе зависимостей

### 1.1. Двоичная трансляция

В индустрии вычислительной техники постоянно возникает потребность в создании новых микропроцессорных архитектур. Причины этой потребности могут быть самыми начиная ОТ необходимости создания более высокопроизводительных различными, вычислительных комплексов И заканчивая академическими исследованиями. Перед разработчиками встаёт вопрос: как обеспечить новый микропроцессор необходимым программным обеспечением (операционной системой, библиотеками, пользовательскими программами и т.д.).

Первый путь – создать всё программное обеспечение заново или перекомпилировать уже имеющиеся из языков высокого уровня. Однако этот путь может влечь за собой большие ресурсные затраты. Далеко не всегда возможно просто взять и перекомпилировать необходимые программы, в особенности для больших программных систем. Как правило, перевод программного обеспечения на новые вычислительные комплексы требует серьёзной работы, называемой портированием программного обеспечения. Например, некоторые части программного обеспечения могут быть написаны на ассемблере и эти части надо полностью переписывать заново. Также в кодах, написанных на языках высокого уровня, могут присутствовать неявные предположения о свойствах архитектуры, для которой они разрабатывались. Например, если программа разрабатывалась для 32-битной архитектуры, то в ней могут присутствовать закладки на то, что адресная переменная имеет размер четыре байта, и при переходе на 64-битную архитектуру это предположение (уже неверное) может привести к ошибке. Возможность возникновения таких ошибок влечёт за собой необходимость полного перетестирования портируемого программного обеспечения. Необходимо проверить весь набор тестов, который запускался перед выпуском финальное версии продукта, а это большие затраты различных ресурсов.

Некоторые части программных продуктов могут быть не доступны в исходных кодах. Например, программа использует библиотеки сторонних разработчиков, которые не распространяются в исходных кодах. В таких случаях надо либо разрабатывать необходимые библиотеки заново, либо заказывать их портирование у авторов. И оба этих варианта требуют дополнительных капиталовложений. Наконец, само используемое программное обеспечение может быть разработано сторонними разработчиками, которые по каким-либо причинам не могут или не будут портировать свои программы.

Второй путь – это поддержка полной аппаратной совместимости микропроцессоров со старыми. Здесь имеется два разветвления. Первое – это развитие новых архитектур на базисе старых. Системы команд новых микропроцессоров полностью включают себя систему команд предыдущих микропроцессоров. Пожалуй, представителем такого подхода являются микропроцессоры с архитектурой х86. Современные сложнейшие x86 микропроцессоры представляют собой чипы. Для повышения производительности, в этих процессорах, начиная с 90-х годов прошлого столетия, используют называемую суперскалярную архитектуру. Внутренне строение микропроцессора постоянно изменяется и развивается. Появляется гораздо больше внутренних (скрытых от пользователя) регистров, сложные исходные команды заменяются на несколько менее сложных, но более быстрых внутренних команд и так далее. Для поддержания совместимости с предыдущими микропроцессорами семейства используется аппаратная перекодировка команд во внутренние, для каждого микропроцессора свои, команды. Поскольку перекодировка происходит динамически, во время исполнения кода, это накладывает существенные ограничения на сложность алгоритмов перекодировки, а следовательно накладывает ограничения и на внутреннюю систему команд микропроцессора. Её нельзя сделать принципиально другой, основанной на других принципах, так как процесс перекодировки займёт слишком МНОГО времени и ЭТО скажется на общей производительности микропроцессора. Также негативно влияет производительность необходимость на поддерживать все команды, которые были использованы в предыдущих микропроцессоров данного семейства. Поддержка этих команд требует дополнительного оборудования, а это не может положительно сказаться на итоговой скорости.

Ещё одним направлением полной аппаратной совместимости является аппаратная реализация старой архитектуры в новой архитектуре, как это сделано в ранних версиях микропроцессора Itanium [16]. В этих микропроцессорах помимо основного ядра с ЕРІС архитектурой, присутствует также простое х86 ядро, которое и обеспечивает совместимость. Однако производительность такого решения оказалась очень низкой и в дальнейшем для второго поколения микропроцессоров Itanium 2 от этого подхода отказались [38].

Получается, что подходы, описанные выше, обладают рядом недостатков и часто не могут быть использованы для перехода на новые микропроцессорные архитектуры или препятствуют быстрому, дешёвому и эффективному переходу. Эти причины породили ещё один подход к обеспечению совместимости — технологию *двоичной трансляции*. Суть этой технологии заключается в разработке программного обеспечения, которое может коды одной платформы (исходная платформа) исполнять на другой платформе (целевая платформа).

Программное обеспечение, которое умеет исполнять коды одной архитектуры на другой архитектуре, появилось очень давно, можно сказать на заре развития вычислительной техники. Эти решения назывались симуляторами. Ещё в 1973 году в "Искусстве программирования, том 1" Кнут описал такой симулятор. Симуляторы исполняют исходный код последовательно, инструкция за инструкцией, моделируя поведение каждой инструкции исходной платформы, инструкциями целевой платформы. Такой подход является очень медленным<sup>1</sup>. Собственно развитие симуляторов и необходимость сделать их более производительными и вылилось в появления двоичной трансляции. Как правило, двоичным транслятором называют систему, которая умеет транслировать код, то есть по двоичному коду исходной архитектуры строить двоичный код целевой архитектуры, выполняющий в точности такие же преобразования. Также двоичный транслятор умеет переиспользовать уже однажды оттранслированный код. То есть если начнёт исполняться участок исходного кода, который уже оттранслирован, то будет использован именно этот уже оттранслированный код.

В настоящее время область применения двоичной трансляции очень широка. Опишем наиболее важные и интересные из них.

Полная двоичная трансляция или двоичная трансляция уровня машины. Такие системы используются для обеспечения полной двоичной совместимости. Через двоичный транслятор проходят все коды исходной архитектуры: базовая система ввода-вывода (BIOS), операционная система, драйвера устройств, системное программное обеспечение, пользовательские приложения и т.д. Для пользователя такой системы её существование абсолютно прозрачно, для него вся работа выглядит также, как если бы это происходило на машине с микропроцессором исходной архитектуры. Пользователь может вообще не знать о том, что он работает с микропроцессором другой архитектуры. В качестве примеров микропроцессоров и используемых вместе с ними систем полной двоичной трансляции можно привести микропроцессоры "Crusoe" и "Efficeon" [39] производимых фирмой Transmeta и систему полной двоичной трансляции для них Code А также отечественные Morphing Software [40]. микропроцессоры [44],[45],[46],[47] и систему полной двоичной трансляции для них Lintel [41],[42],[43]. Для обеих, упомянутых выше систем двоичной трансляции, исходной архитектурой является IA-32 [48]. Одним из последних примеров является микропроцессор Denver

.

<sup>&</sup>lt;sup>1</sup> Как правило, для моделирования требуется много инструкций целевой платформы. Обычно симуляторы затрачивают на исполнение одной инструкции исходной платформы от десятков до сотен тактов целевой платформы. Это конечно оценка в среднем, так как время симуляции очень сильно зависит от сложности исходной и целевой архитектур.

- разработанный компанией Nvidia [112],[113], первое поколение которого выпущено в 2014 года. Исходной архитектурой для Denver является архитектура ARM.

- Двоичный транслятор приложений. Эта группа двоичных трансляторов предназначена для исполнения пользовательских приложений. Операционная система (ОС) для новой архитектуры портируется и двоичный транслятор приложений работает под её управлением. Если в ходе работы ОС происходит запуск приложения в кодах исходной архитектуры, то управления передаётся двоичному транслятору, который уже исполняет данное приложение. Двоичный транслятор может исполнять все непривилегированные команды. Различные системные вызовы исполняются с помощью вызова одного или, если это необходимо, нескольких системных вызовов ОС. Часто для повышения эффективности двоичной трансляции в ОС вносят небольшие доработки. Примерами двоичных трансляторов приложений могут служить IA-32 Execution Layer [49] для исполнения Linux и Windows IA-32 кодов на архитектуре Itanium, а также FX!32 [50],[51],[52] для исполнения Windows IA-32 кодов на архитектуре DEC Alpha.

- Двоичные трансляторы с языков высокого уровня. Двоичные трансляторы с языков высокого уровня схожи с трансляторами приложений описанными выше. Транслятор транслирует код с языка высокого уровня в так называемый bytecode. Этот bytecode не соотвествует никакой реальной архитектуре, реализованной в кремнии. Затем этот байт код с помощью специального программного обеспечения, называемого виртуальной машиной, транслируется в конкретную архитектуру на лету. Наиболее известными представителями являются Java Virtual Machine (JVM) [53], разработанная фирмой Sun Microsystem (сейчас Oracle), Common Language Infrastructure Virtual Execution System (CLI VES) [54] от Microsoft и Dalvik Virtual Machine для операционной системы Android [111]. Отличительной особенностью данных технологий является то, что для новой архитертуры достаточно реализовать транслятор из byte-code и всё существующее программное обеспечение будет работать. Поскольку bytecode не может быть, в силу своей универсальности, просто транслирован в код целевой платформы, то важную роль в производительности bytecode играет эффективный двоичный транслятор, который на выходе будет выдавать качественный результирующий код. Ниже приведены примеры виртуальных машин для bytecode, в которых используют очень развитые двоичные трансляторы: Jalapeno JVM [55],[56], [57], HotSpot JVM [58], JUDO [59].

- Динамическая оптимизирующая трансляция. Такие двоичные трансляторы используются для оптимизации (ускорения) кодов совместимых архитектур. Первый вариант применения это оптимизирующая трансляции, для которой исходная и целевая архитектура одинаковы. Если программа была скомпилирована без применения высоких

уровней оптимизации или вообще без оптимизаций, то динамическая оптимизирующая трансляции может значительно ускорить исполнение этой программы за счёт применения этих оптимизаций. Такой подход был использован в системе Dynamo[60] для архитектуры PA-RISC, DynamoRio[61] для IA-32, Ispike[62] для Itanuim. Второй вариант применения — это оптимизирующая трансляция, для которой целевая архитектура является развитием исходной архитектуры. Например, в микропроцессоры следующего поколения могут быть добавлены новые векторные инструкции (наподобие ММХ и SSE для IA-32 [48]). Использование таких инструкций может значительно ускорить исполнение кода

- Инструментирование и отладочные средства. Часто возникает необходимость получить некоторую информации о процессе исполнения некоторого кода. Это может быть как полная трасса исполнения, так и какая-нибудь специфическая информация, например количество обращений к данной ячейке памяти. Наряду с аппаратной реализацией счётчиков различных событий [17],[48] для этих целей можно использовать двоичную трансляцию. Примерами таких систем являются Shade [63], PIN[104], [105] и valgrind [106], [107].

- Безопасность. Двоичная трансляция также может использоваться для предотвращения различных недоброжелательных атак. Например, для предотвращения атаки с помощью переполнения буфера можно инструментировать код таким образом, чтобы при возврате из процедуры проверялся адрес возврата, и в случае его некорректного значения, программа аварийно завершалась с соответствующей диагностикой. Более подробную информацию по этому вопросу можно почерпнуть из работ [64], [65].

- Виртуализация. Последнее десятилетие активно развивается технология виртуализация, позволяющая на одном компьютере одновременно запускать несколько операционных систем. Для реализации такого запуска на аппаратных платформах без аппаратной поддержки виртуализации или с частичной аппаратной поддержкой виртуализации, одна из операционных систем (host) работает в привилегированном режиме, а остальные (guest) в пользовательском. Из такого разделения возникает необходимость перехватывать привилегированные инструкции guest-системы и моделировать их поведение. Эффективно производить такой перехват можно с помощью двоичной трансляции. Весь привилегированный код guest ОС исполняется под контролем системы виртуализации и, если необходимо, некоторые инструкции транслируются в набор других инструкций, выполняющий эквивалентные действия. Использование двоичной трансляции в системах виртуализации позволяет свести накладные расходы к минимуму [110].

В первых четырёх из описанных выше применений двоичной трансляции крайне важным является не просто транслировать код, но ещё и <u>оптимизировать</u> его. Это связано с тем, что одной из главных задач этих систем является получение высокой производительности.

Для того чтобы двоичный транслятор был эффективным с точки зрения скорости работы транслируемого кода, обычно используется несколько уровней оптимизаторов. Каждый следующий уровень генерирует более оптимальный (с точки зрения времени исполнения) код, но в тоже время затрачивает больше времени на оптимизацию этого кода. Сразу же транслировать код с максимальным уровнем оптимизаций нельзя, так как затраты времени на трансляцию достаточно высоки, а при этом код, который мы оттранслируем, возможно никогда больше не будет исполняться. Для того, чтобы избежать этих, вообще говоря огромных, затрат на трансляцию с большим количеством оптимизаций, при первом исполнении код транслируется очень быстрым транслятором или даже интерпретируется. Но при этом ведётся профилирование этого кода, то есть собирается информация о том, сколько раз исполнилась каждая инструкция. Профилирование ведётся на всех уровнях оптимизаций за исключением самого верхнего (в результате работы которого получается самый быстрый код). На основе профильной информации принимается решение о том, что тот или иной фрагмент кода необходимо перетранслировать с более высоким уровнем оптимизаций [57],[66],[67].

Для того, чтобы двоичный оптимизирующий транслятор был эффективным и оттранслированный код мог по скорости своей работы приближаться к тому же коду, скомпилированному языковым компилятором, необходим мощный оптимизатор верхнего уровня. Этот оптимизатор должен уметь выполнять большинство оптимизаций, которые умеет выполнять языковой компилятор. Однако далеко не каждый алгоритм оптимизации, проводимый оптимизирующим компилятором, может быть просто "скопирован" и перенесён в оптимизатор двоичного транслятора. Это связано со спецификой двоичной трансляции. Пожалуй, главным фактором, ограничивающим алгоритмы, входящие в оптимизирующий двоичный транслятор, является скорость их работы. Эти алгоритмы должны быть очень быстрыми, так как время трансляции кода входит в общее время исполнения программы. Если оптимизатор будет работать очень долго, то весь выигрыш от увеличения скорости работы результирующего кода, может быть перечёркнут временем работы самого оптимизатора. Поэтому многие классические алгоритмы анализа и оптимизаций требуют серьёзной переработки с целью сокращения времени их работы, но при этом необходимо чтобы это не сильно сказалось на качестве результирующего кода.

Ещё одним фактором, из-за которого может потребоваться переработка алгоритмов анализа и оптимизаций, является наличие различных <u>семантических ограничений</u>, введение

которых обусловлено необходимостью повторения точного поведения исходного кода. Ярким примером такого ограничения является проблема восстановления точного контекста<sup>1</sup>. Двоичный транслятор должен быть в состоянии на момент исполнения каждой команды восстановить точный контекст (состояние регистры и памяти) исходного кода, так как в случае возникновения прерывания этот контекст может понадобиться в обработчике прерывания. Такого рода семантические ограничения часто приводят к существенным ограничениям на проводимые оптимизации.

Также в результате разработки двоичного транслятора могут понадобиться специальные оптимизации и алгоритмы, которые либо не нужны, либо их не возможно выполнить в языковых компиляторах. Примерами таких оптимизаций могут служить коррекция профильной информации, использование аппаратной поддержки двоичной трансляции (которое может существенно повысить эффективность результирующих кодов), адаптация к поведению системы<sup>2</sup> и так далее.

Несмотря на упомянутые выше трудности технология оптимизирующей двоичной трансляции позволяет эффективно решить проблему совместимости. Одну из главных ролей в достижении этой цели играет двоичный оптимизирующий транслятор. Однако для достижения высокой эффективности требуется переработка известных алгоритмов анализа и оптимизаций, а также разработка новых алгоритмов анализа и оптимизаций. Это связано с дополнительными требованиями, которые появляются при двоичной трансляции.

### 1.2. Обзор основных особенностей ЕРІС архитектур

Архитектуры с явным выраженной параллельностью на уровне команд (EPIC) имеют возможностью исполнять большое количество операций за такт. Несколько операций исполняющихся за один такт будем называть *инструкцией*. В архитектуре "Эльбрус" в одной инструкции можно одновременно исполнить:

<sup>&</sup>lt;sup>1</sup> Это свойство необходимо в системах полной двоичной трансляции и в системе двоичной трансляции приложений. В других применениях двоичной трансляции часто можно опустить это свойство, сославшись на не поддерживаемую функциональность.

<sup>&</sup>lt;sup>2</sup> Под адапцией к поведению исполняемой программы понимается следующее. В динамическом трансляторе есть возможность применять не всегда корректные преобразования, но при этом необходимо делать динамическую проверку в коде на случай попадания в область некорректного поведения. В случае срабатывания такой проверки динамически производиться перекомпиляция данного участка кода без применения этой оптимизации.

- 6 арифметических операций (из них может быть до 4 чтений из памяти, либо до 2 чтений из памяти и одна запись в память, либо до двух записей в память)<sup>1</sup>

- 3 операции над предикатами

- 1 операцию перехода

- загрузка 4-х 32-битных литерала или 2-х 64-битных

все приведённые классы операций не вытесняют друг друга, то есть в одной команде может одновременно исполниться 6 арифметических операций, 3 операции над предикатами и 1 операция перехода.

В архитектуре Itanium в одной инструкции может исполниться не более шести операций:

- до 6 арифметических операций

- до 2 обращений в память

- до 2 записей в памяти

- до 3 операций перехода

- использовать непосредственно в операции можно только 22-х битные литералы, литералы большой длины необходимо загружать на регистр с помощью специальной операции

Операции работы с предикатами в этой архитектуре явно не присутствуют, но они могут быть смоделированы с помощью специальных арифметических операций сравнения.

Особенностью EPIC архитектур является то, что необходимо явно указывать какие операции будут исполнены в данном инструкции. В силу этого основная работа по достижению высокой производительности ложится на компилятор. Именно компилятор должен расставить операции по инструкциям. Одной из основных задач при компиляции является <u>извлечение максимального параллелизма между операциями</u>. Поскольку может исполняться достаточно много операций одновременно, то, как правило, чем больше параллелизма удастся извлечь, тем быстрее будет исполняться код.

Извлечение параллелизма между операциями настолько важно для высокой производительности ЕРІС архитектур, что в них реализован целый ряд дополнительных механизмов, помогающих лучше распараллеливать код. Часто оказывается возможным извлечь дополнительный параллелизм из программ путём устранения зависимостей (ограничивающими параллельное исполнение) между операциями. Некоторые зависимости нельзя или невозможно устранить только анализами и оптимизациями имеющимися в компиляторе и для их преодоления в микропроцессорах и вводятся специальные механизмы, которые описаны ниже.

<sup>&</sup>lt;sup>1</sup> Оценки приведены без учета возможности исполнять упакованные малоформатные операции, двухэтажные вещественные операции и операции асинхронной подкачки данных из памяти

Спекулятивное исполнение [27]. Спекулятивный режим исполнения позволяет исполнять операции заранее, ещё до передачи управления в то место, где исходно располагалась операция, поэтому такую спекулятивность ещё называют спекулятивностью по управлению. Без использования спекулятивности такое предварительное исполнение возможно далеко не всегда. Аргументы операции могут быть корректны только в случае передачи управления в исходный линейный участок. В случае некорректности аргументов операция может выработать прерывание в месте, в котором изначально программа не предполагала получать прерывание, или вообще выработать прерывание, которое никогда не должно вырабатывается исходной программой. Эти эффекты приводят к неопределённому поведению программы или к её аварийному завершению. Иллюстрацией может служить последовательность из проверки указателя на равенство нулю и, в случае неравенства, чтение по этому указателю 1. Если попытаться осуществить чтение по указателю, до проверки его на равенство нулю, то произойдёт прерывание.<sup>2</sup>

В спекулятивном режиме операция не вырабатывает прерываний. Вместо прерывания в регистр назначения записывается специальный признак, называемый дефектностью, который информирует о том, что операция завершилась аварийно (в не спекулятивном режиме выработалось бы прерывание). Не спекулятивная операция, использующая дефектный аргумент, вырабатывает специальное выделенное прерывание. Спекулятивная операция, использующая дефектный аргумент, вырабатывает дефектность. В случае необходимости в исходном линейном участке можно поставить не спекулятивное использование результата спекулятивной операции, для проявления прерывания.

Предикатное исполнение. Каждая из операций в инструкции может выполняться под некоторым условием. Условие задаётся дополнительным предикатным аргументом, который называется условным аргументом или предикатом операции. Если условный аргумент имеет истинное значение, то операция исполняется так же, как если бы у неё не было предиката. Если условный аргумент ложен, то операция не выполняется и не оказывает никакого эффекта на контекст микропроцессора (регистры, память и т.д.). То есть всё выглядит так, как будто этой операции вообще не было.

Свойство предикатного исполнения позволяет преодолевать ограничения, созданные зависимостями по управлению. В отличие от спекулятивного режима исполнения, зависимости по управлению в этом случае не исчезают, а преобразуются в зависимости по данным. В связи с

20

<sup>1</sup> Классическая организация работы со списком

<sup>&</sup>lt;sup>2</sup> В большинстве современных микропроцессоров

этим часто процесс построения предикатного кода называют преобразования зависимостей по управлению в зависимости по данным.

Спекулятивность по данным. Часто зависимостями, ограничивающими параллельность, являются зависимости между операциями записи в память и операциями чтения из памяти, которые потенциально конфликтуют по адресу. То есть для операций не удаётся доказать различие адресов обращений в память по всем возможным путям исполнения. Для возможности исполнения чтения раньше записи в аппаратуре заводится специальный буфер адресов. Также заводятся специальные операции чтения из памяти с занесением в буфер адреса, по которому производится считывание. Для проверки заводятся операции передачи управления в случае отсутствия нужного адреса в буфере. Для всех операций записи в память производится проверка на пересечения адреса, по которому осуществляется запись, с элементами буфера. Все элементы буфера, пересекающиеся с адресом записи, удаляются. В архитектуре "Эльбрус" такой буфер называется DAM (disambiguation access memory). В архитектуре IA-64 — ALAT (Advanced Load Address Table).

Применение спекулятивности по данным осуществляется следующим образом. Операция чтения преобразуется в операцию с занесением в буфер и переносится выше потенциально конфликтующей записи. В месте исходного расположения операции чтения строится операция проверки с передачей управления в специально созданный компенсирующий код. В случае, если адреса записи и чтения пересекутся, соответствующий элемент из буфера вычёркивается и операция проверки передаст управление на компенсирующий код. В компенсирующем коде производится перевыполнение операции чтения, и всех операций, зависящих от неё и выполненных до перехода в компенсирующий код. Затем управление возвращается обратно в точку вызова компенсирующего кода.

### 1.3. Обзор внутреннего представления в компиляторе

#### 1.3.1. Внутреннее представление

**Определение.** Линейным участком называется блок операций, имеющий только одну точку входа — первую операцию блока и содержащий только одну операцию передачи управления, возможно условную, и эта операция является последней в блоке.

Внутри линейного участка выполнение операций идёт последовательно, без передачи управления, от первой операции до последней операции. Если операция передачи управления безусловная, то из линейного участка возможен только один выход — на целевой линейный участок операции передачи оправления. Если операция передачи управления условная, то возможны два выхода. Первый — на линейный участок, являющийся целевым для операции

передачи управления, в случае, когда условие истинно. Второй — на линейный участок следующий непосредственно за данным, в случае, когда условие ложно. Такой тип выхода называется провалом.

**Определение.** Графом потока управления (или просто графом управления) называется направленный граф, который представляет все возможные передачи управления между линейными участками. Узлы графа управления соответствуют линейным участкам, а дуги – путям передачи управления.

Узлы и дуги графа управления могут содержать профильную информацию, которая описывает число исполнений линейного участка и число передач управления по дуге.

**Определение.** Совокупность всех операций, всех линейных участков и графа управления называется промежуточным представлением (Intermediate Representation).

Промежуточное представление служит для отображения всей семантики программы или её части (модуля, процедуры, региона) во время всего процесса работы компилятора. Входные данные компилятора (программы на языке высокого уровня для языкового компилятора, двоичный код для двоичного транслятора) сразу преобразуются в промежуточное представление, и дальнейшая работа идёт уже с ним. Атомарным элементом промежуточного представления является операция. Операция преобразует некоторые входные данные в выходные. В сущности, она соответствует одной операции в микропроцессоре, однако бывают операции, у которых нет аналогов в системе команд микропроцессора, но они служат для отображения дополнительной информации для компилятора.

**Определение.** Гиперблоком называется подграф графа управления объединённый в один узел с помощью предикатного исполнения. Гиперблок имеет только один внешний вход, и может иметь много выходов.

**Определение.** Графом потока данных называется надстройка над промежуточным представлением такая, что для каждого аргумента операции отображается, какая операция может выработать этот аргумент. Узлами графа являются аргументы и результаты операций.

Потоковых последователей операции можно разделить на два класса:

- Операция b является npямым потоковым последователем операции a, если b может использовать только значение, выработанное a, и это не зависит от пути, по которому мы пришли в a.

- Операция b является he npямым потоковым последователем операции a, если рассматриваемый аргумент b может определяться ещё и другими операциями, помимо

a. Значение, используемое в операции b определяется в зависимости от пути в графе управления, по которому мы в неё пришли.

**Определение.** Компонентой потокового графа называется любой максимально связанный подграф графа потока данных.

При дальнейшем изложении будут использоваться некоторые фрагменты промежуточного представления. Введём следующий формат записи для операций:

```

<uмя> [спекулятивность] [[арг.]...] [->результат] [предикат]

```

где

<имя> – имя операции. Например, для операции сложения это ADD и так далее.

[спекулятивность] – признак, что операция исполняется в спекулятивном режиме.

[[арг.]...] - аргументы операции. У операции может быть произвольное количество аргументов. Количество аргументов зависит от имени операции. В качестве аргументов может быть константа, обозначаемая своим значением. Также в качестве аргументов могут быть использованы виртуальные регистры. Это объекты, которые используются во внутреннем представлении компилятора. Их свойства соответствуют физическим регистрам, имеющимся в микропроцессоре. Количество виртуальных регистров неограниченно. Виртуальный регистр обозначается Vsn, где n, натуральное число, его номер, например Vs15. Перед генерацией кода отдельной фазой виртуальные регистры распределяются на физические регистры. Также аргументом операции может являться виртуальные предикаты. Их свойства аналогичны свойствам виртуальных регистров. У виртуальных предикатов есть дополнительное свойство, называемое маской. Истинная маска обозначает, что для управления выполнением операции будет взято само значение предиката, а ложная маска означает, что будет взято логическое отрицание значения предиката. Виртуальный предикат обозначается Pn [M], где n, натуральное число, его номер, в квадратных скобках описывается маска предиката, символ Т (от английского true) обозначает истинную маску, символ F (от английского false) обозначает ложную маску.

[->результат] – результат операции. Результатом операции может являться либо виртуальный регистр, либо виртуальный предикат.

[предикат] — управляющий предикат операции (условный аргумент). Предикат, который определяет, выполнится операция или нет.

Для иллюстрации приведём несколько примеров.

эта запись означает операцию сложения виртуального регистра под номером два, с константой три и результат записывается в виртуальный регистр под номером пять. Данная операция не является спекулятивной и она выполняется безусловно. Ещё один пример:

эта запись означает операцию сложения виртуального регистра под номером двадцать с виртуальным регистром под номером четырнадцать, а результат записывается в виртуальный регистр под номером восемь. Операция является спекулятивной. Операция выполняется только, если виртуальный предикат под номером три является ложным.

В Таблица 1 приведено описание операций, которые будут использоваться в дальнейшем изложении, а также время их исполнения в тактах (количество тактов через которое готов результат операции и его можно использовать в других операциях). Время указывается по отношению ко всем потребителям, если не оговорено противное. Выбранные времена не описывают некоторую существующую архитектуру, но они выбраны близкими к тем временам, которые встречаются в реальных архитектурах.

| Имя      | Краткое описание операции               | Время исполнения операции в |

|----------|-----------------------------------------|-----------------------------|

| операции |                                         | тактах                      |

| ADD      | сложение двух аргументов                | 1                           |

| SUB      | вычитание из первого аргумента второго  | 1                           |

| MOV      | пересылка первого аргумента в результат | 1                           |

| SHL      | сдвиг влево первого аргумента на        | 1                           |

|          | значение второго аргумента              |                             |

| OR       | побитовое логическое "или" двух         | 1                           |

|          | аргументов                              |                             |

| AND      | побитовое логическое "и" двух           | 1                           |

|          | аргументов                              |                             |

| CMP      | сравнение на равенство двух аргументов  | 2                           |

| CMPL     | сравнение на меньше двух аргументов     | 2                           |

| MUL      | умножение двух аргументов               | 4                           |

| LD      | чтение из памяти по адресу равному    | 31      |

|---------|---------------------------------------|---------|

|         | сумме значений первого и второго      |         |

|         | аргумента                             |         |

| ST      | запись в память значения третьего     | $0^2$   |

|         | аргумента, по адресу равному сумме    |         |

|         | значений первого и второго аргументов |         |

| BRANCH  | операция передачи управления на метку | $1^3$   |

| LD.lock | операция чтения из памяти плюс        | $3/0^4$ |

|         | занесение в таблицу DAM               |         |

| LD.chk  | операция проверки в таблице DAM       | 1       |

Таблица 1. Описание операций и времени их исполнения.

### 1.3.2. Граф зависимостей

Над операциями промежуточного представления можно построить граф зависимостей.

**Определение.** Граф зависимостей — это ориентированный ациклический граф, узлами которого являются операции промежуточного представления. Дуга соединяет две операции тогда и только тогда, когда операция — предшественник дуги по некоторой причине должна выполниться не позже операции — последователя дуги. Дуги графа зависимостей также будем называть *зависимостями*.

Все причины появления зависимостей между операциями определяются алгоритмом построения графа зависимостей, который фактически анализирует каждую пару операций на предмет наличия между ними зависимости того или иного типа [18]. Фактически граф зависимостей вводит частичный порядок между операциями. Ниже приведены несколько причин, по которым могут упорядочиваться операции:

<sup>1</sup> В современных микропроцессорах время исполнения операции чтения из памяти зависит от того

тактов.

находится ли в данная ячейка данных в кэше или нет, и может колебаться от нескольких тактов до нескольких сотен тактов. Этот фактор достаточно трудно учитывать при проведении оптимизаций и везде далее, если не оговорено противное, будем считать, что читаемая ячейка находится в кэше первого уровня и время исполнения операции равно трём тактам.

<sup>&</sup>lt;sup>2</sup> Так как операция ST не вырабатывает результата, то исходное определение времени исполнения теряет свой смысл, однако будем считать, что операции чтения из памяти доступно записанное значение в том же такте. Порядок выполнения записей в память и чтений из памяти внутри одной команды определяется порядком устройств на которых исполняются операции.

<sup>3</sup> В следующем такте выполнение продолжается с метки

$<sup>^4</sup>$  Время чтения из памяти такое же как и операции LD – три такта; время занесения в таблицу DAM – ноль

- Потоковые зависимости это использование результата одной операции в качестве аргумента другой.

- Антизависимости это переопределение ресурса занимаемого аргументом одной операции, под результат другой операции

- Зависимость по результату или output-зависимость переназначение ресурса, отданного под результат одной операции, под результат другой.

- Предикатные зависимости потоковая зависимость в случае, когда аргументом является условный предикат операции

- Зависимость между обращениями в память по потенциально пересекающимся адресам (кроме случая чтение-чтение). Термин потенциально пересекающиеся адреса означает, что не удалось доказать, что адреса не пересекаются по всем путям программы.

- Зависимости по управлению это зависимости между операциями передачи управления и другими операциями. Например, операция находящаяся в линейном участке должна выполнить до операции передачи управления.

Это далеко не все типы зависимостей, которые могут возникнуть. Набор всех возможных причин, по которым операции необходимо упорядочить, определяется несколькими факторами. В первую очередь архитектура микропроцессора может вводить те или иные ограничения на порядок операций. Например, в архитектурах поддерживающих предикатное исполнение, присутствует особый тип потоковой зависимости — предикатная потоковая зависимость по условному аргументу. Ещё одним фактором, который влияет на набор зависимостей, являются условия, в которых строится граф зависимостей. Под условиями понимается компилятор, производящий построение, и опции, с которыми он запущен. Так, например, специфическими для двоичной трансляции являются зависимости между всеми операциями записи в память.

Граф зависимостей является взвешенным графом. Каждая дуга графа зависимостей имеет *длину*, которая определяет через сколько тактов после того, как выполнился предшественник дуги, может начаться выполнение последователя дуги. Например, большинство операций целочисленной арифметики исполняются за один такт, а операции вещественной арифметики — за несколько тактов. Так как граф зависимостей является ациклическим, найдётся хотя бы одна вершина, в которую не входит ни одна дуга, и хотя бы одна вершина, из которой не выходит ни одной дуги. Добавим к графу две вершины называемые ENTER и END. Построим дуги, соединяющие ENTER со всеми вершинами, в которые не входит дуга, а также дуги, соединяющие все вершины, из которых не выходят дуги, с узлом END. В дальнейшем будем рассматривать только такие расширенные графы зависимости.

**Определение.** Длиной пути в графе зависимостей называется сумма длин всех дуг входящих в этот путь.

**Определение.** Высотой графа зависимостей называется максимальная длина пути ведущего от ENTER-а к END-у.

Фактически, высота графа зависимостей есть минимальная длительность исполнения данного фрагмента кода микропроцессором заданной архитектуры, сократить которую уже невозможно. Однако, если количество операций, которые могут выполнится в одной инструкции, достаточно велико, то высота графа зависимостей и будет характеризовать то время, за которое исполнится данный код.

**Определение.** Критическими путями называются пути в графе зависимостей, имеющие максимальную длину.

**Определение.** Временем раннего планирования узла графа зависимостей называется максимальная из длин всех путей, ведущих от узла ENTER к данному узлу.

**Определение.** Если взять время раннего выхода из узла вычесть из него длину пути от некоторого узла графа до этого выхода и взять минимум этих величин по всем путям и всем выходам, то полученная величина называется временем позднего планирования этого узла графа.

Время раннего планирования операции соответствует первому такту, в который можно спланировать операцию. Раньше спланировать её нельзя, так как не будут выдержаны задержки в графе зависимостей. Время позднего планирования операции это такой такт, до которого (включительно) необходимо спланировать операцию, чтобы не изменилась общая длина вычислений.

### 1.3.3. Особенности графа зависимостей в динамическом двоичном трансляторе

При построение графа зависимостей в динамическом двоичном трансляторе на промежуточном представлении полученном из двоичного кода возникает гораздо больше зависимостей, чем при построение графа зависимостей на представлении полученном из языка высокого уровня. Большинство из этих зависимостей ложные, то есть на самом деле этих зависимостей нет, но транслятор не может доказать их отсутствие и поэтому вынужден их строить. Возникновение большего числа зависимостей в двоичном трансляторе является следствием того, что в двоичном коде (а следовательно и в промежуточном представлении полученном из этого кода) содержится гораздо меньше информации о семантике исходной

программы, чем в коде языка высокого уровня. Опишем подробнее основные причины возникновения большего числа зависимостей и типы зависимостей возникающих зависимостей.

Первой причиной является отсутствие в двоичном коде информации об объектах, по которым производятся обращения в память. Рассмотрим пример кода на языке Си:

```

void f(int *a, int *b)

{

...

a[i] = t;

r = b[i];

...

}

void g()

{

a = malloc( SIZE);

b = malloc( SIZE);

f(a, b);

}

```

Компилятор с языка Си может определить, что в функцию f подаются параметры полученные двумя разными вызовами функции malloc, и следовательно эти две области памяти не пересекаются. Получив такую информацию компилятор может переставлять между собой обращения к массиву a и обращения к массиву b. После компиляции рассмотренного фрагмента в двоичный код данная информация теряется. Двоичный транслятор в некоторых случаях может определить, что объекты a и b получены как результат вызова функции с названием malloc, однако даже в этом случае он не может делать никаких предположений относительно её результата — это может быть пользовательская функция, у которой просто название совпадает с общепринятым malloc-ом, а результат её совсем другой. Итак в результате отсутствия информации об объектах, по которым производятся обращения в память, в двоичном трансляторе появляется больше зависимостей между обращениями в память.

Перейдём к рассмотрению второй причины. В динамическом двоичном трансляторе время трансляции кода входит в общее время исполнения программы, поэтому оптимизируются только самые горячие участки кода. В силу этого инициализирующие записи в некоторые переменные (регистры, ячейки памяти) могут не попасть в транслируемую область, и

транслятор ничего не будет знать о взаимосвязи между этими переменными. Рассмотрим следующий пример промежуточного представления:

```

MOV 0x80000000 -> Vs1

MOV 0x80000010 -> Vs2

...

<много другого кода>

...

ST Vs1 0 Vs3

LD Vs2 0 -> Vs4

```

Если в транслируемую область попали операции ST и LD, но не попали операции MOV, то транслятор не сможет доказать, что операции ST и LD независимы и между ними будет построена зависимость. Итак в результате ограниченности области трансляции в динамическом двоичном трансляторе появляется больше зависимостей между обращениями в память.

Третья причина — маленькое количество регистров. Данное свойство присуще не всем микропроцессорным архитектурам. Однако в рамках данной работы исследование проводилось для двоичного транслятора с исходной архитектурой х86 и результирующей "Эльбрус", а в архитектуре х86 относительно мало регистров. Маленькое количество регистров приводит к необходимости их часто переиспользовать. Такое переиспользование порождает лишние антизависимости, которых нет по семантике исходной программы. В архитектуре "Эльбрус" гораздо больше регистров, и следовательно нет необходимости в таких антизависимостях и от них можно избавиться.

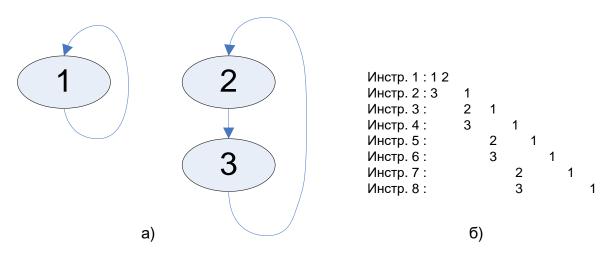

Четвёртая причина — недостаток информации о времени жизни регистров. В подавляющем большинстве случаев время жизни регистра заканчивается на последнем использовании. Однако во многих архитектурах, в том числе и в х86, есть возможность прочитать значения регистров в обработчике прерывания, в том числе и в обработчике асинхронного прерывания, которое может прийти практически в любой момент. В силу этого свойства время жизни регистра заканчивается только тогда, когда этот регистр будет перезаписан, а не в момент последнего использования. Рассмотрим пример изображённый на Рис. 1 и покажем как недостаток информации о времени жизни регистров может привести к ложным предикатным зависимостям.

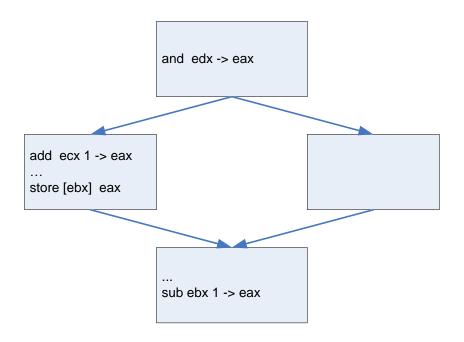

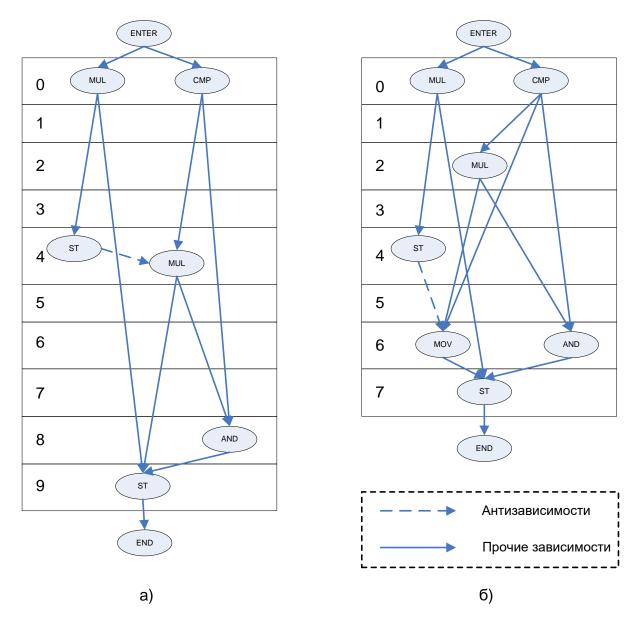

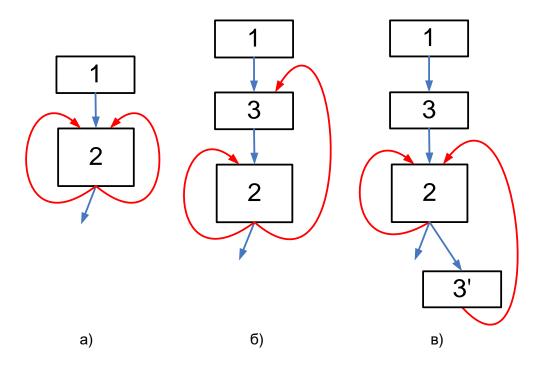

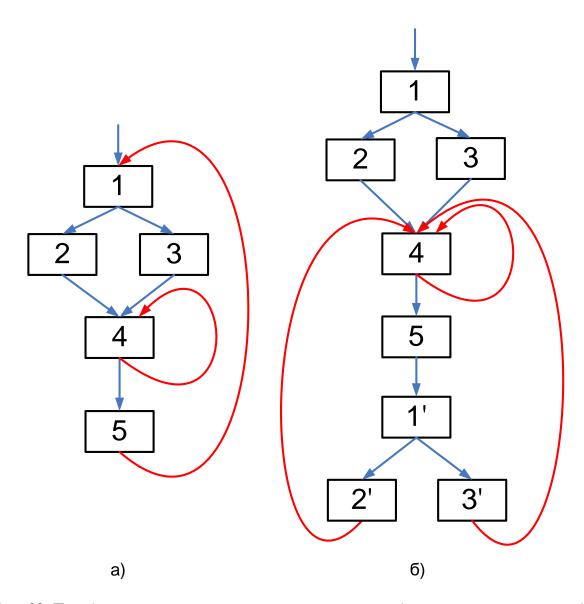

**Рис. 1.** Пример как недостаток информации о времени жизни регистров приводит к возникновению ложных предикатных зависимостей.

Время жизни результата операции add, по семантике программы, заканчивает на операции store, так как это последнее использование. Однако за счёт того, что регистр может потенциально быть использован в обработчике прерывания необходимо продлить время его жизни до операции sub. Заметим также, что до операции sub доживает также результат операции and (по правой ветви). Предположим теперь, что мы хотим переместить операцию add в верхний узел. Если бы нам не надо было продлять время жизни регистра, то можно было бы поступить следующим образом. Заменить результат операции add на другой, нигде больше не используемый регистр, а также все использования результата операции add заменить на этот новый регистр. После такого преобразования можно перенести add в верхний узел не ставя эту операцию под предикат ветвления, при этом бы программа оставалась корректной. Однако в силу того, что результат операции add используется в начале нижнего узла, а также в силу того, что в начале нижнего узла регистр еах может быть определён как операцией add так и операцией and, мы не можем заменить результат add на новый регистр. Следовательно при переносе операции add в верхний узел её надо поставить под предикат ветвления, создав таким образом "не обязательную" предикатную зависимость.

Выше были описаны четыре причины, по которым при трансляции двоичного кода возникает больше зависимостей, чем в случае компиляции с языка высокого уровня. Это далеко не все причины, однако целью данного раздела является не классификация всех возможных причин и отличий, а демонстрация того, что при трансляции двоичного кода возникает больше

"не обязательных" зависимостей, чем в случае компиляции с языка высокого уровня. Таким образом в динамическом двоичном трансляторе для достижения высокой скорости работы результирующего кода необходимо уделять большое внимание алгоритмам и методам борьбы с ложными зависимостями.

# 1.4. Ускорение результирующего кода за счёт сокращения длины критических путей

Как уже отмечалось выше, одной из главных задач оптимизирующего компилятора для EPIC архитектур является распараллеливание кода. Часто оказывается выгодным даже построить лишнею операцию, при этом сократив высоту вычислений. Для новой операции найдётся свободное место в одной из инструкций, а высота вычислений уменьшится, и код будет работать быстрее. В двоичном оптимизирующем трансляторе эта задача ещё более актуальна в силу большого количества ложных зависимостей, мешающих распараллеливанию. Существует ряд методов способных сократить длину критических путей. Мы разделим рассмотрение этих методов на два класса. Первый – методы применяемые в ациклических областях, второй – методы применяемые в циклических областях.

### 1.4.1. Ациклические области

# 1.4.1.1. Классические оптимизации с точки зрения сокращения длины критических путей

Многие классические оптимизации сокращают длину критических путей, но в силу своей важности и различия между собой получили собственные названия [33], [34]. Примерами могут служить построение предикатного кода (if-conversion), advanced unroll и многие другие. Рассмотрим несколько примеров более подробно.

Первый пример оптимизация основанная на применение различных *алгебраических тождеств*. Рассмотрим следующую последовательность операций:

```

E=0 ENTER

E=0 ADD Vs1 Vs2 -> Vs3

E=1 SUB Vs3 Vs2 -> Vs4

E=1 END

```

Она эквивалентна следующей последовательности $^1$ :

$<sup>^{1}</sup>$  При условии, что регистр  ${\tt Vs3}$  больше нигде не используется.

```

E=0 ENTER

E=0 ADD Vs1 0 -> Vs4

E=0 END

```

Здесь запись E=1 перед операцией обозначает время раннего планирования операции. В результате такого преобразования, во-первых, уменьшилось количество операций. Во-вторых, уменьшилась и высота вычислений с двух до одного такта.

Часто среди тождественных преобразований выделяют преобразования, которые получили название *понижения силы операций* (operator strength reduction) [22]. Простейшим примером может являться преобразование 2×х в х+х или в х<<1. Развитием этой техники является применение понижение силы операций к индуктивным переменным. Часто в литературе понижением силы операций называют именно оптимизацию индуктивных переменных. Классическим примером применения понижения силы операций к индуктивным переменным является работа с массивом в цикле. Рассмотрим следующий фрагмент кода:

```

K(int * a, int x, int s)

i = 0;

do

{

a[x+i*s] = 0;

i++;

} while ( i < 100);</pre>

```

промежуточное представление для этого фрагмента будет выглядеть следующим образом

```

VOM

\Omega

-> Vs1

loop:

Vs1 s

E=0 MUL

-> Vs2

E=4

Vs2 x

-> Vs3

ADD

E=5

SHL

Vs3

2

-> Vs4

E=6 ST

Vs4

a

0

E=0 ADD

Vs1

1

-> Vs1

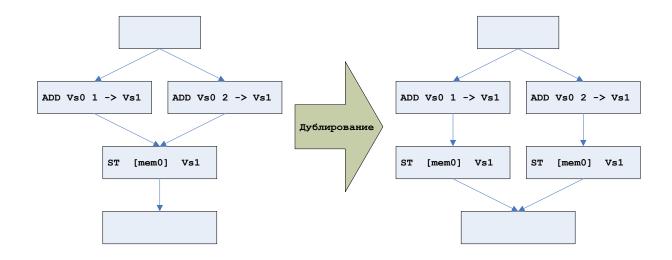

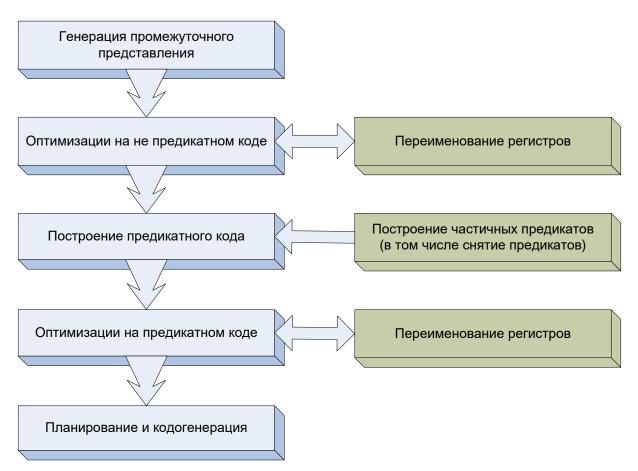

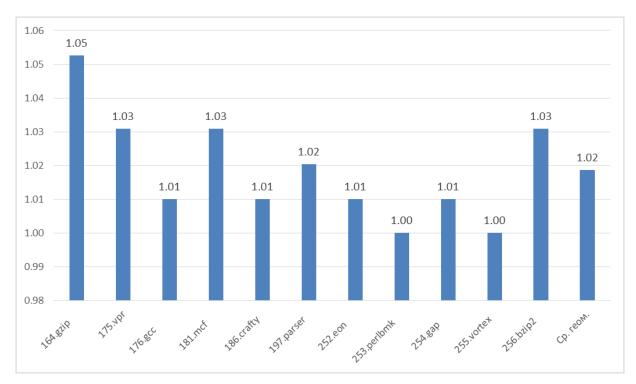

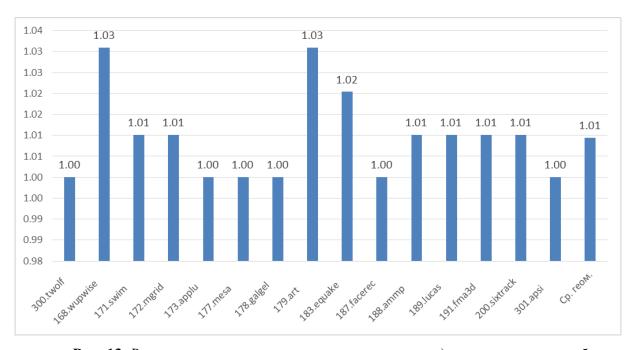

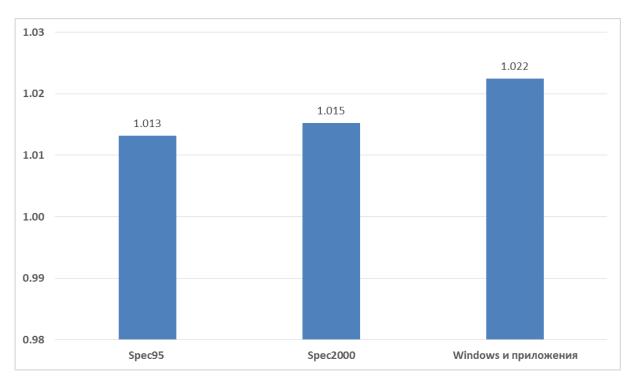

Vs1