# Генерация тестовых данных для покрытия путей в формальных спецификациях системы команд

Коцыняк Артём Михайлович kotsynyak@ispras.ru

Научный руководитель: к.ф.-м.н. Камкин Александр Сергеевич

### Схема создания микропроцессора

- Требования

- HDL-описание

- □ VHDL, Verilog

- Готовая схема

### Верификация микропроцессоров

Экспертиза

Формальная верификация

- Имитационное тестирование

- □ модульное (сигналы)

- □ системное (тестовые программы)

### Генерация тестовых программ

- Случайная

- На основе тестовых шаблонов

- генерация тестовых последовательностей

- □ генерация тестовых данных

- На основе моделей

### Генерация тестовых данных

- Случайная

- Комбинаторная

- На основе ограничений

# Использование формальных спецификаций системы команд

- Автоматическое извлечение тестовых ситуаций

- □ ветви логики операций

- □ условия выполнения операций

Метрики тестового покрытия

# Подход MicroTESK к генерации тестовых программ

- Генерация тестов по шаблонам

- Использование модели микропроцессора

- Использование формальных спецификаций для моделирования (nML/Sim-nML)

- Язык описания архитектуры

- Система команд описывается иерархической структурой

# м

#### Структура формализма nML/Sim-nML

# Спецификация ресурсов микропроцессора на nML/Sim-nML

```

Константы:

Метки:

let REGBITS = 5

let byte order = "big"

let PC = "NIA"

Типы данных:

let SP = "GPR[29]"

type bit = card(1)

type byte_t = card(8)

Регистры:

type halfword = card(16)

reg GPR [2 ** REGBITS, long t]

type word = card(32)

reg NIA [1, address]

type long_t = int(32)

reg LO [1, long t]

type address = card(32)

reg HI [1, long t]

type index = card(REGBITS)

Глобальные переменные:

Память:

mem CIA [1, address]

mem M[2 ** 31, byte t]

mem branch [1, bit]

mem JMPADDR [1, address]

```

# Спецификация режимов адресации на nML/Sim-nML

```

Регистры:

mode\ REG(r:index) = GPR[r]

syntax = format("$%d", r)

image = format("%5b", r)

Константы:

mode IMM16(n : int(16)) = n

syntax = format("%d", n)

image = format("%16b", n)

mode IMM26(n : int(26)) = n

syntax = format("%d", n)

image = format("%26b", n)

```

```

Группы операций (структура):

Точка входа:

op instruction(op: instr kind) op instr kind = alu instr

syntax = op.syntax

load store instr

branch_instr

image = op.image

jump instr

action = {

CIA = NIA;

branch == 0 then

op alu instr = arith instr

logic instr

NIA = CIA + 4;

else

op arith instr = ADD

NIA = JMPADDR;

branch = 0;

SUB

ADDI

endif;

op.action;

GPR[0] = 0;

op logic_instr = AND

0R

NOR

```

```

Операция сложения (ADD):

var tmp unsigned word [1, card(32)] // Временная переменная

var overflow bit[1, bit]

// Временная переменная

op ADD (rd: REG, rs: REG, rt: REG)

syntax = format ("ADD %s, %s, %s", rd.syntax, rs.syntax, rt.syntax)

image = format ("000000%s%s%s%s%11b", rs.image, rt.image, rd.image, 32)

action = {

overflow bit::tmp unsigned word = rs + rt;

if overflow bit == 1 then

SignalException("Integer Overflow Exception");

else

rd = tmp unsigned word;

endif;

```

```

Операция условного перехода (BEQ):

var tmp signed word [1, int(32)] // Временная переменная

op BEQ (rs : REG, rt : REG, offset : IMM16)

syntax = format ("BEQ %s, %s, %s", rs.syntax, rt.syntax, offset.syntax)

image = format ("000100%s%s%s", rs.image, rt.image, offset.image)

action = {

if rs == rt then

branch = 1;

tmp signed word = offset;

tmp signed word = tmp signed word << 2;

JMPADDR = NIA + tmp_signed_word;

endif:

```

```

Операция подсчёта ведущих нулей (CLZ):

var tmp signed byte [1, int(8)] // Временная переменная

op CLZ(rd: index, rs: REG)

syntax = format ("CLZ %d, %s", rd, rs.syntax)

image = format ("011100%s%5b%5b%11b", rs.image, rd, rd, 33)

action = { tmp signed byte = 31; GPR [rd] = 32; loop; }

loop = {

if tmp_signed_byte >= 0 then

if rs<tmp signed byte..tmp signed byte> == 0 then

tmp_signed byte = tmp_signed byte - 1:

else

GPR[rd] = 31 - tmp signed byte;

tmp signed byte = -1;

endif;

loop;

endif:

```

## Свойства кода спецификации

- Простые условия ветвления

- Циклы с небольшим максимальным числом итераций

- Пути в коде являются тестовыми ситуациями

# Извлечение путей выполнения из спецификации системы команд

- Построение полного кода операции

- □ обход иерархии инструкций

- □ определение входных данных

- преобразование режимов адресации

- □ раскрутка циклов

- Построение предикатов для путей

- Определение побочных эффектов

# .

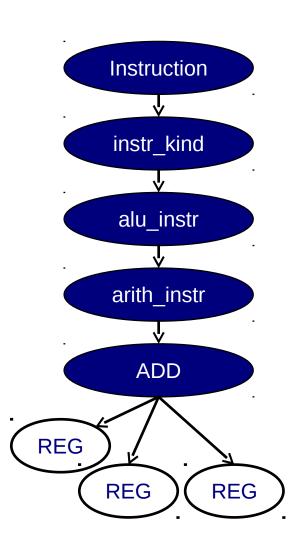

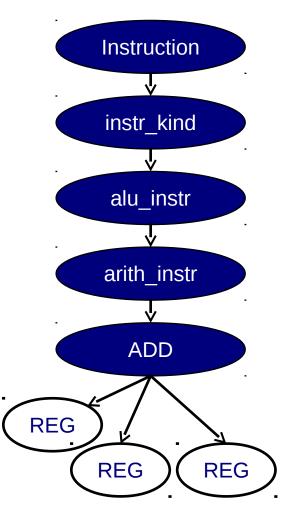

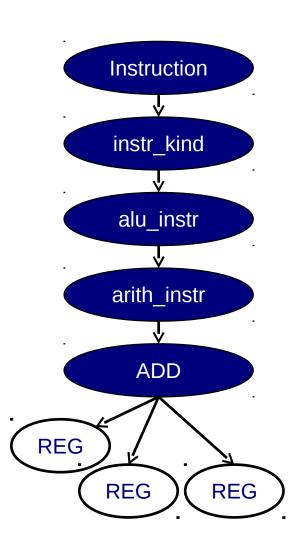

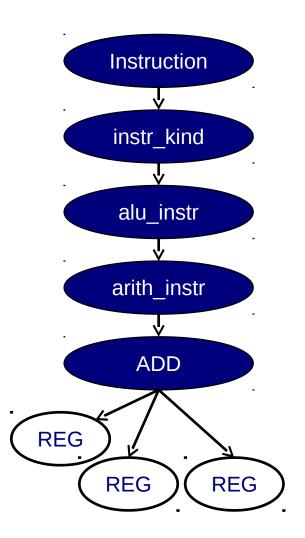

# Обход иерархии инструкций

#### Определение входных данных

```

op ADD (rd : REG, rs : REG, rt : REG)

image = format ("000000%s%s%s%s%11b",

rs.image, rt.image, rd.image, 32)

mode\ REG(r:index) = GPR[r]

image = format("%5b", r)

op ADD (rd : index, rs : index, rt : index)

image = format ("000000%5b%5b%5b%11b",

rs, rt, rd, 32)

```

### Построение полного кода инструкции

```

op ADD (rd : index, rs : index, rt : index)

action = {

CIA = NIA;

if branch == 0 then

NIA = CIA + 4;

else

NIA = JMPADDR;

branch = 0;

endif;

overflow_bit::tmp_unsigned_word = GPR[rs] + GPR[rt];

if overflow bit == 1 then

SignalException("Integer Overflow Exception");

else

GPR[rd] = tmp unsigned word;

endif;

GPR[0] = 0;

```

### Построение предикатов для путей

```

op ADD (rd : index, rs : index, rt : index)

action = {

CIA = NIA;

if branch == 0 then

NIA = CIA + 4;

else

NIA = JMPADDR;

branch = 0;

endif;

overflow_bit::tmp_unsigned_word = GPR[rs] + GPR[rt];

if overflow bit == 1 then

SignalException("Integer Overflow Exception");

else

GPR[rd] = tmp unsigned word;

endif;

GPR[0] = 0;

```

### Построение предикатов для путей

- $branch_0 = 0 \land overflow\_bit_0::tmp\_unsigned\_word_0 = GPR[rs]_0 + GPR[rt]_0 \land overflow\_bit_0 = 1$

- $branch_0 \neq 0 \land overflow\_bit_0::tmp\_unsigned\_word_0 = GPR[rs]_0 + GPR[rt]_0 \land overflow\_bit_0 = 1$

- $branch_0 = 0 \land overflow\_bit_0::tmp\_unsigned\_word_0 = GPR[rs]_0 + GPR[rt]_0 \land overflow\_bit_0 \neq 1$

- $branch_0 \neq 0 \land overflow\_bit_0::tmp\_unsigned\_word_0 = GPR[rs]_0 + GPR[rt]_0 \land overflow\_bit_0 \neq 1$

### Определение побочных эффектов

```

Instruction

instr_kind

alu_instr

arith_instr

ADD

REG

REG

REG

```

```

op ADD (rd : index, rs : index, rt : index)

action = {

CIA = NIA;

if branch == 0 then

NIA = CIA + 4;

else

NIA = JMPADDR;

|branch = 0|

endif;

overflow_bit::tmp_unsigned_word = GPR[rs] + GPR[rt];

if overflow bit == 1 then

SignalException("Integer Overflow Exception");

else

GPR[rd] = tmp_unsigned_word;

endif;

GPR[0] = 0;

```

# 1

### Определение побочных эффектов

```

branch_0 = 0 \land overflow\_bit_0::tmp\_unsigned\_word_0 = GPR[rs]_0 + GPR[rt]_0 \land overflow\_bit_0 = 1 ==> NIA_1 = NIA_0 + 4 \land GPR[rd]_1 = tmp\_unsigned\_word_0 \land GPR[0]_1 = 0

```

```

branch_0 \neq 0 \land overflow\_bit_0::tmp\_unsigned\_word_0 = GPR[rs]_0 + GPR[rt]_0 \land overflow\_bit_0 = 1 ==> NIA_1 = JMPADDR_0 \land branch_1 = 0 \land GPR[rd]_1 = tmp\_unsigned\_word_0 \land GPR[0]_1 = 0

```

$branch_0 = 0 \land overflow\_bit_0::tmp\_unsigned\_word_0 = GPR[rs]_0 + GPR[rt]_0 \land overflow\_bit_0$  $\neq 1 ==> NIA_1 = NIA_0 + 4 \land exception("Integer Overflow Exception") \land GPR[0]_1 = 0$

branch<sub>0</sub>  $\neq$  0  $\wedge$  overflow\_bit<sub>0</sub>::tmp\_unsigned\_word<sub>0</sub> = GPR[rs]<sub>0</sub> + GPR[rt]<sub>0</sub>  $\wedge$  overflow\_bit<sub>0</sub>  $\neq$  1 ==> NIA<sub>1</sub> = JMPADDR<sub>0</sub>  $\wedge$  branch<sub>1</sub> = 0  $\wedge$  exception("Integer Overflow Exception")  $\wedge$  GPR[0]<sub>1</sub> = 0

# Стратегии генерации тестовых данных

- Несколько наборов данных для заданной тестовой последовательности

- Набор данных с максимальным покрытием путей в данной тестовой последовательности

- Отслеживание общего покрытия путей в наборе тестовых последовательностей

#### Генерация тестовых данных

- Построение ограничений шаблона

- Поиск путей с требуемыми эффектами

- Использование информации о покрытии

- □ Поиск нерассмотренных выполнимых путей

- □ Ограничения путей добавляются к ограничениям шаблона

- Использование решателей ограничений для генерации данных

### Проблемы

- Определение побочных эффектов

- □ nML/Sim-nML var vs. mem

- □ Вызов внешних функций

- Внутренние механизмы процессора

- □ Подсистема управления памятью

- Модуль управления переходами

- □ Конвейер

# Дальнейшие планы

- Использование модели конвейера

- Создание базы тестовых знаний

- □ Объединение подходов к генерации данных

- □ Переиспользование тестового знания

#### Спасибо за внимание!