Развитие полупроводниковых технологий и постоянное совершенствование компьютерных архитектур сделали организацию микропроцессоров настолько сложной, что при их разработке делаются тысячи (!) ошибок. Избежать просчетов не удается даже таким крупным компаниям, как Intel и AMD. Ошибки в сложных проектах неизбежны, главное — уметь их быстро обнаруживать и не давать "распространяться" в микросхемы. Это и является основной задачей верификации.

## ЧТО ТАКОЕ ВЕРИФИКАЦИЯ?

Верификациейназываетсяпроверкасоответствиярезультатов, полученных наотдельных этапах проектирования, требованиямиограничениям, установленным дляних напредыдущих этапах. На начальном этапепроверяют, соответствуют лирезультатыи сходным требованиям (техническом узаданию). Основная задачаверификации—контролькачества проектирования, включаятакие его аспекты, как функциональная корректность, надежность, удобствои спользования имногие другие [1]. В рамках этой стать и рассматривается лишьодна составляющая верификации—проверка соответствия результатов проектирования функциональным требованиямили, другими словами, функциональная верификация. В дальней шем длякраткости будем называть функциональную верификацию просто верификацией.

Посколькуфункциональностьмикропроцессораопределяетсяреализуемойимсистемойкоманд, то, вобщихсловах, задачаверификациисостоитвпроверкетого, чтомикропроцессор (точнее, егопроектнаямодель) реализует все указанные в техническом задании команды, причемрезультат выполнения каждой изних вовсех допустимых ситуациях является корректным (соответствует заданным функциональным требованиям). Еслипроектная модельрасходится стребованиями, говорят, чтоимеет местоошибка проектирования. Принятие решения отом, какиечасти проекта (модельмикропроцессора, документация ит.п.) подлежат исправлению, является от дельной задачей, не входящей в верификацию. Частооши бочной является проверяемая модель, и именноее после локализации оши бки исправляют.

А. Камкин, к.ф.-м.н. kamkin@ispras.ru

Помимовыявления дефектов (ошибок и недоработок в проекте), верификация решает еще несколько очень важных задач, втомчисле определяет наиболеекритичные и наиболее подверженные ошибкам подсистемы и предоставляет всем за интересованным лицаминформацию отекущем состояний проекта [1]. Такимобразом, верификация—это не простопой скошибок в микропроцессоре, асложная система обратных связей в процессе проектирования, которая позволяет своевременно оценки эффективно управлять проектом.

Верификация при проектировании микропроцессоров

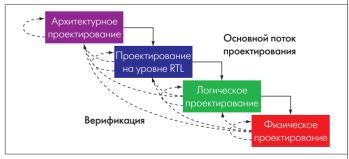

Напомнимкратко, какустроенпроцесспроектированиямикропроцессоров. Исходнуюинформацию дляпроекта даеттехническое задание, вкоторомописаныразличные характеристикира зрабатываемого устройства: функциональность, производительность, интерфейссвнешними устройствами, конструктивные ограничения и др. Микропроцессор проектируют в четыре основных этапа, результатом каждого изкоторых являетсямодельна определенном уровне абстракции. Это архитектурное проектирование, проектирование на уровнерегистровых передач, логическое проектирование и физическое проектирование (рис. 1).

Наэтапеархитектурногопроектированияуточняютсясистемакомандмикропроцессораиегомикроархитектура. На данномэтапевкачествеосновногосредстваприменяют языкипрограммирования общегоназначения (C, C++), языкисистемногопроектирования (System C, System Verilog) испециализированные языки описания архитектуры (nML, LISA). В результатеархитектурногопроектирования, помимо уточнения требований к процессоруи создания соответствующей документации, создается программный симулятор (эмулятор), к оторый позволяетинтер претировать программы, написанные дляцелевого микропроцессора.

Наследующемэтапе—этапепроектированиянауровнерегистровых передач (RTL, Register Transfer Level)—с помощьюязыка описания аппаратуры (VHDL, Verilog) предельно точноописываетсялогическаяструктураифункционирование схемымикропроцессора. Результатом RTL-проектирования въляется модель уровнярегистровых передач (RTL-модель), которая спотактовой точностью описывает пересылки данных, возникающие при работе модулей микропроцессора.

Врамкахлогическогопроектированиясоздаетсясхемаиз логическихвентилейв заданномтехнологическомбазисе, котораяфункциональноэквивалентна RTL-модели, разработанной напредыдущем этапе. Данный этапполностью автоматизирован, хотяиног дасхему дорабатывают вручную в целях оптимизации и повышени я уровнятестируемости (testability). Построение логической схемы длямодели уровнярегистровых передач называется логическим синтезом.

Наэтапефизическогопроектированияпроизводятразмещениеитрассировкутопологиисхемынакристалледлязаданногонабораограничений(взаимноерасположениеэлементовсхемы, площадых ристалла, минимальноерасстояниемеждупроводниками, размерпроводникаит.п.). Этапфизического проектирования (физический синтез), также, какипредшествующийему этаплогическогопроектирования, автоматизирован средствами САПР.

Строгоговоря, верификация присутствует навсех перечисленных этапах, но в первую очередь—на уровнерегистровых передач. Этосвязаностем, что RTL-модельразрабатывается вручную мириксирует функциональность схемы, а последующие процессы логического и физического синтеза эту функциональность не изменяют (точнее, не должны изменять). В ажной составляющей верификации, которая не отражена на представленной схеме, является верификация на кристалле" (post-silicon verification), которую можно провести, только когда появляются первые опытные образцыми кропроцессора (так называемые образцы Ао). Использование микросхем в место программных моделей существенно ускоряет процесс проверки, однаконе позволяет контролировать в сесигналыми кропроцессора, что ухудшает качество верификации.

Рис. 1. Обобщенная схема процесса проектирования микропроцессора

На ошибках учатся

Опыт проектированиямикропроцессоров, накопленный десятилетиями, говорит, что верификацию нельзяигнорировать илиуделятьей маловнимания—последствия ошибок проектирования могут быть катастрофическими.

Пожалуй, самойизвестнойошибкойвмикропроцессоре является" Pentium FDIV bug" — ошибкавкоманде делениячи-селсплавающейточкоймикропроцессора Pentium, разработанногокомпанией Intel[2] (онабыла обнаружена в 1994 году). Ошибка возника еттолько вочень редких случаях (биты с пятого по десятый мантиссы делителя должны быть равные динице, а биты с первого почет вертый — принимать одноиз пяти определенных значений)[3]. Вероятность проявления данной ошибки на случайных числах очень мала, но, тем неменее, онабыла найдена. Ее обнаружил профессорматематики Томас Найсли, заметивнеточность в научных расчетах. В результате, несмотрянато, что большинства пользователей эта ошибка не касалась, Intel пришлось заменитьмикропроцессоры с ошибкой, что обошлось ей в 475 млн. долл.

Описаннаяошибка—наиболееизвестна, ноонадалеко неединственнаявсвоемроде—"багов" вмикропроцессорах "живет" достаточномного, идажесамаятщательнаяверификация(приразумных ограничениях наресурсы) непозволяет обнаружить их все. Например, в процессоре Pentium II сначала продажбыло найдено более 500 шибок. Задачей верификации, в современном понимании, является не создание безошибочной микросхемы, авыпускра ботоспособного инадежного продукта.

Производителиизвлекают урокиизсвоих ошибокистараются не повторятьих. Да, после скандальной ошибки в PentiumIntelсделаланесколькоошибок, касающихсяарифметикисплавающейточкой (вчастности, "Dan-0411bug"), однакосейчаскомпания проверяет арифметические модули (FPU, Floating Point Units) всехразрабатывае мыхмикропроцессоров спомощью формальных методов (ометодах верификации будет краткорасска занониже). В частности, при верификации Pentium 4 были обнаружены две серьезные ошибки в FPU: в командах сложения и умножения. Боб Бентли, руководитель работ поверификации этогомикропроцессора, отмечает, что еслибы не формальные методы, указанные ошибки, вероятно, таки остались бы не обнаруженными, что в полнемогло привести к ситуации 1994 года [4].

## Сложность верификации

Верификациямикропроцессоров—процессоченьтрудоемкий, а, следовательно, очень дорогостоящий. Согласно Дженику Бергерону, авторитетномуспециалистуизкомпании Synopsys, затратына верификацию составляют около 70% от всех усилийнара зработку процессора; числоинженеров-верификаторовобычнов двоепревосходитчислоинженеров, проектирующих RTL-модель, аисходный кодтестов, проверяющих систе-

<sup>\*</sup> Сейчас ведутся исследования и уже есть промышленные разработки по так называемому поведенческому или высокоуровневому синтезу (HLS, High-Level Synthesis) — автоматическому построению RTL-моделей из высокоуровневых описаний (например, на SystemC или С/С++). Если при проектировании микропроцессора используются инструменты поведенческого синтеза (например, Cynthesizer или Synphony HLS), основным объектом верификации становятся модели, разработанные на этапе архитектурного (поведенческого) проектирования.

му,составляет до8о% от общего объемаразработанного кода [5]. Сростом сложности (закон Мураработает досих пор) положениет олько ухудшается. Если этицифрымалочтого ворят вам, скажем проще верификация современного микропроцессора общего назначения—это сотничеловек, тысячиком пьютеров и миллионы долларов ежегодно.

Сложностьверификациисвязанасогромнымчисломситуаций, возможных вработемикропроцессора. Наегофункционированиевлияют командыпрограммы, ихрасположениев памяти, значения операндов, генерируемые исключения, зависимостимежду командами, состояния подсистеми многое другое. Помножьте это на длинные конвейеры, переупорядочивание команд, спекулятивноевы полнение и другие архитектурные изыски и выполучите "практически невыполнимую задачу" [6]. Факторов, от которых зависит поведение микропроцессора, оченьмного, ночислоих комбинаций практически бесконечно.

Дляиллюстрацииэтогоположениярассмотримошибку вотносительнопростомпосовременныммеркаммикропроцессореMIPSR4000PC/SC(1994год)[7].Ошибкапроявляет-СЯТОЛЬКОВ СЛЕДУЮЩЕЙ СИТУАЦИИ: КОМАНДАЗАГРУЗКИ ДАННЫХИЗ оперативнойпамятиврегистрвызывает промахвкэше данных;занейчерезодну"пустую" командупор(NoOPeration) следуетбезусловный переход поадресу, содержащем усяв за-ГРУЖЕННОМРЕГИСТРЕ;КОМАНДАПЕРЕХОДА—ПОСЛЕДНЯЯКОМАНДА настраницевиртуальнойпамяти;номерследующейстраницы несодержитсявбуферетрансляцииадресов(TLB, Translation LookasideBuffer).ВмикропроцессорахархитектурыМIPSимеетсятакназываемыйслот задержкиперехода.Этоозначает, чтоинструкция, следующая запереходом (в данном случаенаходящаясянаследующейстранице), должнабытывыполненавместесинструкциейперехода.Поэтомуврассматриваемомпримерепривыполненииинструкциипереходавозникает исключение TLBMiss, связанноеспромахом(отсутствиемномерастраницы)в Т.В.Ошибкавмикропроцессорезаключает-СЯВТОМ, ЧТОПРИВОЗНИКНОВЕНИИИСКЛЮЧЕНИЯ УПРАВЛЕНИЕПЕредаетсяненапредопределенный адресобработчика исключений, анаадрес, покоторому осуществлялся переход. Ниже приведеншаблонпрограммынаязыкеассемблера, вызывающей эту ошибку.

```

Iw г, ... // промах в кэше данных пор // одна команда NOP јг г // команда перехода ... // началостраницывиртуальнойпамяти, // которой нет в TLB.

```

Пример демонстрирует, чтоприверификациимикропроцессоровнеобходимоучитыватьмножествофакторов, некоторыеизкоторых, напервыйвзгляд, могут показатьсяникакне связанными другс другом. Многие серьезные ошибкиможно обнаружить лишь приодновременном выполнениинескольких нетривиальных условий. Длябольшейэффективностиобнаруженияошибокиупрощенияихлокализацииверификациямикропроцессоравключаетвсебяверификациюотдельныхмодулей(этореализация принципа"разделяйивластвуй" — основногоподходаборьбы сосложностью). Дляопределенияправильностиработымодуляиспользуетсянетехническое задание намикропроцессорвцелом, апроектные документы, описывающие функции именноэтогомодуля. Такимобразом, проверкамикропроцессоровосуществляетсяна двухосновных уровнях: модульном исистемном. Указанное деление на уровниявляется относительным, например, микропроцессорможет быть частью болеесложной системы, амодульпредставлять системуизболее простых блоков.

## МЕТОДЫ ВЕРИФИКАЦИИ

Методыверификацииможноразделитьнатриосновных класса:экспертизу, имитационноетестирование иформальную верификацию. Более подробную классификацию методов верификацииможно найтивработе [1], мыже ограничим ся указаннымитремя. Помимо этих методов существую так называемые синтетические илигибридные методы [8], использующие комбинацииразных подходов. Так, в отдельный классвы делилисьметодытестирования, использующие элементы формальных методов — тестирование на основе моделей.

Кэкспертизе относятся методы верификации, в которых оценкарезультатов проектирования выполняется людьми путемне посредственного анализа. От других методов экспертизуютличает возможность выполнятьее, используятолькорезультаты проектирования, а неих формальные модели (как в формальной верификации) илирезультаты работы (как в имитационном тестировании). Экспертиза позволяет выявлять практически любые виды ошибок, причем на самых ранних стадиях. В тоже время она неможет быть автомати зирована и требует активного участиялю дей. Различные от четы показывают, чтоот 50 до 90% всех зафиксированных вжизненном циклеоши бок может быть обнаружено спомощью экспертиз, однако эффективность экспертизы существенно зависит от опыта и мотивации ее участников.

Имитационнымтестированиемназываетсятестирование моделей, полученных наразных этапах проектирования. Для краткостибудемназыватымитационноетестированиепростотестированием, хотяследует понимать, чтоподтестированиемобычнопонимают проверкумикросхемна предмет наличиятех нологических ошибок (обрывов проводников, замыканий ит.п.), что, безусловно, верификацией неявляется. Для применениятестирования необходимоиметь работающую модельмикропроцессораилих отябынекоторых модулей, поэтомутестирование нелыз яиспользовать наранних фазах проектирования. Для проведения тестирования требуется дополнительная подготовка: созданиетестовираз работ катестовой системы, позволяющей их выполнять. Созданиетестов, позвоситемы, позволяющей их выполнять. Созданиетестов, позво-

ляющихполучитьадекватнуюоценкукачествасложногомикропроцессора, являетсятрудоемкой задачей, требующей достаточноглубокогопониманиятехнического задания изнания особенностей реализации процессора.

Формальныеметодыверификациииспользуютформальныемоделимикропроцессоровиихмодулей. Этомогутбыть логические или алгебраические модели, моделина основе графовиликонечных автоматов, атакже модели других типов. Анализформальных моделей выполняется с помощью специфических техник, таких как проверка моделей (инструменты SMV, Magellan, Formality), автоматизированное доказательствотеорем (HOLLight, ACL2, PVS), проверка эквивалентности (Conformal, Formality, Formal Pro). Указанные техники позволяют автоматически проверить соответствие моделисистемы формальным спецификациям. Подформальными пецификациями понимаютсяма шиночитаемые (допускающие автоматическую обработку) представления требований к верифицируемой системе.

Формальныеметодыспособныобнаруживатьсложные ошибки, практическиневыявляемые с помощью экспертиз илитестирования. Разумеется, чтобыприменять формальныеметоды, необходимопостроить модели, чтовесьматрудоемко. Крометого, формализовать требования кмикропроцессорной системеможнотолько приееглубоком понимании, а значит—необходим тщательней шийанализсистемы, выполняемый совместноспециалистами поформальным методам и разработчиками.

### Применение на практике

Наразных этапах проектирования могутиспользоваться разные методыверификации. Например, наначальных стадиях, когда уточняется техническое задание и формируется документация, может применяться экспертиза; на этапах архитектурного проектирования и проектирования на уровне RTL—имитационное тестирование; на этапелогического проектирования — формальная верификация.

Самымраспространеннымметодом, которыйиспользуют всепроизводителимикропроцессоров, являетсятестирование. Экспертизавтойилиинойстепенитакжеприсутствует вбольшинствепроектов. Чтокасаетсяформальной верификации, ее могутпозволить себелишь достаточнокрупные компании (Intel, AMD, IBM, Motorola), ноиониприменяют еетолько для сравнительно небольших подсистем. Формальные методыс ложноприменять вусловиях изменяющего сяпроекта, поэтому, как правило, онииспользуются напоздних этапах проектирования. Компания Intel в ложила громадные средства в развитиемето доврегрессионной проверки формальных доказательств [9] (приизмененииструктуры схемынужно зановоперестраивать системутеорем и лемм, а их число может достигать десятки тысяч).

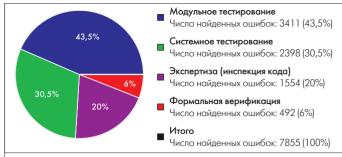

Числонайденныхошибокзависит от методаверификации (рис.2).Видно, чтобольшинствоошибок (74%) находится спо-

Рис. 2. Метод верификации — число найденных ошибок (Pentium 4)

мощьютестирования, причемоколо60% изних приходится на модульноетестирование. Поскольку формальные методы применяются вограниченных масштабах (в Pentium 4 такимобразом были проверены модуль арифметики с плавающей точкой имодуль декодирования команд), процентоши бок, най денных с их использованием, невелик (6%), носрединих есть такие, которые сложнооб наружить, применя ятестирование или экспертизу. Приверификации FPU Pentium 4 было най дено около 20 таких оши бок.

Рис. 3. Основные типы ошибок проектирования (Pentium 4)

Рис. 4. Схема имитационного тестирования (а) и структура тестовой системы (б)

Типы ошибок в микропроцессорах

Нанашвзгляд, интереспредставляет нетолькоколичествообнаруженныхошибок, нотакжеихтипы. Согласно[9], более 75% ошибок, обнаруженных припроектировании Pentium 4, можно отнестик 12 типам (рис. 3). Отметим, что некоторые из этихтиповочень похожи, поэтому четкой границымеждуниминет.

## Подробнее о тестировании

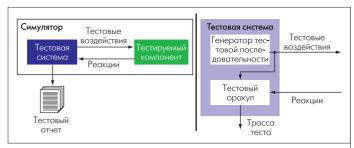

Посколькуимитационноетестированиеявляетсясамымраспространеннымподходомкверификации, остановимсяна немподробнее.В дальнейшемподтестируемымкомпонентомбудемпониматьлибомодельмикропроцессоравцелом, либомодельотдельногомодуля. Длятестированиянеобходиматестоваясистема (рис. 4а)—специализированнаяпрограмма, написаннаянатомжеязыке, чтоитестируемыйкомпонент (Verilog, VHDL), наязыке программирования общегоназначения (C, C++), либонаспециализированномязыке верификации аппаратуры (OpenVera, SystemVerilog). В некоторойстепеникактестовуюсистемуможнорассматривать программу, написанную на ассемблере илиязыке высокого уровня, которая послекомпиляции и загрузкив память выполняетсямоделью микропроцессора (тестирование спомощью тестовых программ) [10].

Работатестовой системы и тестируемого компонентапроисходит в симуляторе. Тестовая система подает на тестируемый компоненттестовые воздействия (устанавливая входные сигналыили, еслитестовой системой является программа, создавая спомощью командопределенные ситуации вработеми кропроцессора) и осуществляет проверку правильностире акцийнаних (считывая выходные сигналыили проверя значения регистров). В процессе тестирования тестовой системой создается тестовый отчет (трасса теста), который используется для анализа оши боки оценки полноты тестирования.

В общемслучаетестоваясистемарешает три основные задачи: генерирует тестовую последовательность, проверяет правильность поведения тестируемого компонента, оценивает полноту тестирования. Сучетом этогоразбиения тестирования на задачи обычно детализирую тархитектуру тестовой системы, различая в ней такие компоненты, как генератор тестовой последовательностии тестовый оракул (рис. 46).

Такаяархитектуратестовойсистемыприменимакак дляаппаратного, таки дляпрограммного обеспечения. Например, онаиспользуетсявтехнологиитестирования UniTESK, разработанной в ИСПРАН[11, 12]. Современные методологии верификации аппаратуры, в частности, OVM (Open Verification Methodology), предлагают дополнительную детализацию компонентов тестовой системы [13].

Генератортестовой последовательности создает последовательность тестовых воздействий, накоторой проверяют поведениетестируемого компонента. Онразрабатывает сята-кимобразом, чтобы создавать разнообразные сценарии работы тестируемого компонента.

Тестовый оракулоценивает соответствие поведениятестируемого компонентатре бованиям к нему и выносит вердикт обих соответствии или несоответствии. Тестовые воздействия, реакции, атакже свой вердикт оракул записывает в тестовый отчет. Еслитестовая системареализована в в иде программы, рольтестового оракулавы полняют специальные команды этой программы, проверяющие з начения регистров микропроцессора послевы полнения команд тестового воздействия [10].

Внастоящеевремясуществуетмножествометодовтестирования, которые по-разному подходят к генерациитестовой последовательности, проверке правильности поведения и оценке полнотытестирования. Рассмотрим современные подходы к решению этих основных задачтестирования.

Генерациятестовойпоследовательности. Качествотестированиянапрямую зависит от используемых тестовых последовательностей (оттого, насколько полноони охватывают ситуации, возможные вработе микропроцессора; какие взаимодействиямеждуегомодулямивызывают). Для построения тестовых последовательностей применяют несколько основных методов, средикоторых ручная разработка, случай ная генерация, генерация на основе шаблонов и генерация тестов на основе конечных автоматов.

Ручнаяразработкатестов до сих пориспользуется на практике, хотя долятестов, разработанных вручную, постепенно снижается. "Вручную" проверяют "тонкие" ситуации вработемикропроцессора, описание и создание которых сложно формализовать.

Самымраспространенными" дешевым" методомавтоматического построениятестов является случайная генерация. Несмотряна простоту, "случайные тесты" позволяют быстрообнаруживать значительное числооши бок в проекте. Крометого, онимогут создавать ситуации, которые сложно предугадать заранее, нокоторые, темнеменее, интересны для тестирования. Наиболее известный коммерческий генератор случайных тестов длямикро процессоров—инструмент RAVEN, разработанный компанией Obsidian Software [14].

Развитием случайной генерации тестов стала генерация на основеша блонов. Шаблоном называет слабстрактное

представлениетеста, вкоторомвместоконкретных значений входных параметров (операндовкомандиливходовмодуля) указывают ограничения, которымони должны соответствовать. Генератор, используя механизмразрешения ограничений, строит случай ноезначение, удовлетворяющее заданной системе условий. Подходна основеша блонов поддерживается, например, в генераторах тестовых программ Genesys-Pro (IBMR esearch) [15] и Місто ТЕЅК (ИСПРАН) [12]. В последнем, крометого, есть поддержка автоматической генерациитестовых шаблонов на основе комбинаторных техник.

Конечныеавтоматыявляютсяширокоиспользуемымформализмомдляпредставленияаппаратных системичастоиспользуются длягенерациитестовой последовательности. Как правило, тестыстроятся путемобхода графа состояний автоматной моделитестируемого компонента. Автоматная модельможет разрабатываться вручную, строиться на основе статического анализакода RTL-моделили бона основе формальных спецификаций. На использовании автоматных моделей для построения тестовых последовательностей базируется, вчастности, технология UniTESK и поддерживающие ее инструменты [11].

Проверкаправильностиповедения. Дажееслитестовые последовательностиохватывают всеситуациивработетестируемогокомпонента, ошибкиневозможнообнаружить, непроанализировав поведениекомпонента. Существуеттриосновных методапроверки правильности поведения: ко-симуляция, самопроверяющие тесты и формальные спецификации.

Дляко-симуляцииотдельнооттестируемогокомпонентаразрабатываютегоисполнимуюмодель,котораяимеетту жефункциональность,нопредставленавболееабстрактной форме(эталоннаямодель).Язык,накоторомразрабатываетсяэталоннаямодель, может отличатьсяот языкаразработки тестируемогокомпонента.Натестируемыйкомпонентиэталоннуюмодельподаетсяоднаитажетестоваяпоследовательность, результаты работы компонента и модели сравнивают насоответствие. Еслинаходится несоответствиемеждуповедениемтестируемогокомпонентаиэталонноймодели,выясняют,какаямодельнекорректна.Послеисправления ошибкитестированиепродолжается.Достоинствоко-симуляциивтом, чтопроверкаправильностиповедения компонента производится автоматически. Таким образом, можно задействоватьавтоматическиегенераторытестов,чтоповышаетэффективность тестирования.

Когдатестынужнополучитьбыстро, вместоко-симуляции применяют подходподназванием самопроверяющиетесты. Данный способпредполагает, что каждый тест, помимотестовой последовательности, содержит проверки, которые необходимопровести послеили вовремя воздействия накомпонент. Содной стороны, прииспользовании самопроверяющих тестов ненужна эталонна ямодель, но, с другой стороны, требуются большие усилия наразработ кутестов, поскольку

ихнеобходимоснабдитьсоответствующимипроверками. Автоматическая генерациятестовых последовательностей для самопроверяющих тестов практическине возможна. Другой существенный недостаток подхода—сложность сопровож дениятестов: приизменении тестируемого компонента приходится переделывать в сетесты, связанные сизмененной функциональностью.

Наконец, третий способпроверки правильности поведенияоснованнаиспользованииформальных спецификаций(машиночитаемогопредставлениятребованийктестируемомукомпоненту). Частнымслучаемформальных спецификацийявляетсяэталоннаямодель,используемаядля ко-симуляции(этоисполнимаяспецификация). Другойразновидностьюспецификацийявляются декларативные спецификации, которые описывают требования в виденабораограничений (утверждений), которым должно удовлетворятьповедениетестируемогокомпонента.Примерамиявляютсяконтрактныеспецификациивформепред-ипостусловий[16]испецификации, основанные натемпоральной логике(OpenVeraAssertions, SystemVerilogAssertions, Property SpecificationLanguage).Какико-симуляция,подходнаосновеформальных спецификаций сочетается савтоматическим построениемтестовых последовательностей, приэтомразработатьдекларативныеспецификациичащебывает проще, чем исполнимую модель.

Оценкаполнотытестирования. Очевидно, чтополный переборвсевозможных значений входных сигналов привсевозможных состояниях микропроцессораневозможени, вообщеговоря, ненужен (такоетестированиея вляется избыточным). Напрактике нужен методоценки полнотытестирования — критерий, который на основезначений некоторых метрик позволяет определить, когдаможно за вершаты проектирование и приступать к производству.

Одинизнаиболее" древних" методовоценки полноты тестирования основаннаи змерении частоты обнаружения ошибок. Когдачастота становится достаточно низкой и сохраняется такой в течение длительного времени, можно заканчивать тестирование. Методкажется устаревшим, но в сочетании с другими подходами он активнои спользуется современными производителями микропроцессоров.

Естьи другой подход, когдаметрики полноты тестирования определяют на основеко да RTL-моделимикропроцессора или формальной спецификации—такие метрики называются структурными и функциональными, соответственно. Идея этогомето да состоит в следующем. На основе кода определяется набортестовых ситуаций, которые в совокупностисоставляют метрику тестового покрытия. Самыми звестными структурными метрикамиявляются покрытие операторов (тестовой ситуацией з десьявляется срабатывание того или иного оператора, заданного в коде RTL-модели), покрытие путей (каждая ситуация соответствует определенно-

мупутивыполнения) ипокрытиевыражений (здесьтестовой ситуацией является определенная комбинация значений истинности условий, входящих влогическое выражение). Критерием полноты тестирования обычноя вляется достижение 100%-ного покрытия ситуаций врамках выбранной метрики.

Дляспецификаций, поскольку этокоднанекоторомязыке, такжеможноиспользовать указанные метрики. Висполнимых спецификациях оценивают преимущественно покрытиеграфапотока управления (покрытие путей), ав декларативных — покрытие условий вограничениях, описывающих требования (покрытие выражений). Важное достоинство функциональных метрик в том, что они базируются натребованиях к тестируемомуком поненту, и ихможнои спользовать для в сехреализаций с одной и той же функциональностью.

Напрактике для оценки полноты тестирования используют комбинированные подходы, учитывающие разные показатели. Например, компания Motorolau спользует следующую совокупность критериев для прекращения тестирования изапуска чипа в производство [4]:

- необнаруженоошибокпривыполнении 40 10 Р тактов случайных тестов;

- выполнен план верификации;

- достигнутыцели, заданныеструктурнымиифункциональными метриками;

- наблюдаетсяустойчивоеуменьшениечастотыобнаружения ошибок;

- на календаре наступила определенная дата.

Несмотрянато, чтометодыверификациинепрерывносовершенствуются, ониедвапоспевают запостояннымусложнениеммикропроцессоров. Еслипервые устройствамогпроверить буквально одинчеловек путемнепосредственного анализасхем, тосейчаскомандыинженеров-верификаторов достигают внушительных размеров. Так, основакоманды, занимавшейся проверкой процессора Pentium Pro, состояла из 10 человек, в проекте Pentium 4 к ним присоединилосьеще 6 оинженеров [9]. У нас нетточных данных относительнотекущего состояния дел, но, скореевсего, сейчас счет идет на сотни. Трудоемкость верификациимикропроцессоров просто поражает — тольконаформальную проверку Pentium 4 было затрачено 6 очеловеко-лет [4], в целом же затраты на верификацию составляют несколько сотен человеко-лет!

Мечтамногихпроизводителеймикропроцессоров—автоматическое доказательствокорректностипроекта. Однаков ближайшейперспективепрорывавэтойобластинепредвидится. Скореевсего, формальныеметоды, какираньше, будут применятьсялишь длянаиболеекритичных подсистем (хотявполне закономерно, чточислоисложность таких подсистем будет постепенноувеличиваться). Основным способом верификации пока остается тестирование, нонужно отметить, что современные методытестированиямногое заимствуют изформальных методов (например, использованием атематических методов для построениятестовыхпоследовательностейиприменениеформальныхспецификаций,дляпроверкиправильностиповедения). Скореевсего, вскоромбудущемнасожидаетещеболеетесная интеграция разных методов верификации.

## ЛИТЕРАТУРА

- 1. Кулямин В. Методы верификации программного обеспечения, 2008 www.ispras.ru/~kuliamin/docs/ VerMethods-2008-ru.pdf.

- 2. Beizer B. The Pentium Bug An Industry Watershed. Testing Techniques Newsletter, TTN Online Edition, September 1995.

- 3. Coe T., Tang P.T.P. It Takes Six Ones to Reach a Flaw.

- Chinese University of Hong Kong. Technical Report 95-5(61), 1995.

- 4. N. Mokhoff. Intel, Motorola Report Formal Verification Gains. EE Times, 06/21/2001.

- 5. Bergeron J. Writing Testbenches: Functional Verification of HDL Models. Kluwer Academic Publishers, 2000.

- 6. Корниленко Д.Д. Проверка на дорогах. www. ixbt.com/cpu/cpu validation.html.

- 7. MIPS R4000PC/SC Errata, Processor Revision 2.2 and 3.0. MIPS Technologies Inc., 1994, May 10.

- 8. Bhadra J., Abadir M., Ray S., Wang L. A Survey of Hybrid Techniques for Functional Verification. IEEE Design & Test, 2007, v. 24, № 22, p. 112—122.

- 9. Bentley B. Validating the Intel Pentium 4 Microprocessor. DAC 2001: Design Automation Conference, 2001, p. 244–248.

- 10. Камкин А.С. Генерация тестовых программ для микропроцессоров. Труды Института системного программирования РАН, 2008, т. 14, ч. 2, с. 23—63.

- 11. Сайт, посвященный технологии тестирования UniTESK. – www.unitesk.com.

- 12. Сайт, посвященный исследованиям в области верификации аппаратуры, проводимым в ИСП PAH. hardware.ispras.ru.

- 13. Сайт, посвященный методологии OVM. www. ovmworld.org.

- 14. Страница, посвященная генератору RAVEN. www.obsidiansoft.com/products-and-services/ inroducing-raven/.

- 15. Страница, посвященная генератору Genesys-Pro. — www.haifa.ibm.com/projects/verification/ genesys\_pro/index.shtml.

- 16. Иванников В.П., Камкин А.С., Косачев А.С., Кулямин В.В., Петренко А.К. Использование контрактных спецификаций для представления требований и функционального тестирования моделей аппаратуры. Программирование, 2007, №5, с. 47—61.

## 32-разрядный микроконтроллер рекордно малых размеров

КомпанияNXPSemiconductorsобъявилаовыпускеопытныхобразцов 32-разрядногомикроконтроллеранабазепроцессора Cortex-МотипаLPC1102,монтируемыхвультракомпактныйкорпус WL-CSP размером 2,17×2,32×0,6 мм.

Новаямодель LPC 1102, входящая в семействомикроконтроллеров LPC 1100 компании, имеет ключевые характеристики этого семейства—низкую потребляемую мощность (неболее 13 ом A/МГ цвактивном режиме), высокую производительность и обширную функциональность. Поутверждению разработчиков, благодарявы сокой производительности, простоте применения, малому энергопотреблению и, что особенноважно, значительном ууменьшению размеракода для 8-/16-бит приложений новый микроконтроллер значительно проще применять, чем существующие 8-/16-бит устройства.

ВмикросхемуLPC1102входят 32-Кбайт флеш-памятьи 8-Кбайт ОЗУ, четырехканальный 10-битный АЦП, приемопередатчик UART интерфейс SPI, два 32-битных таймера, два 16-битных таймера и один 24-битный системный таймер. Крометого, вмикросхемереализована поддержка SWD-отладки ипрограммирования счетырым эточками прерывания и двумя точками наблюдения. Для обеспечения максимальной гибкос-

тивсеодиннадцатьфункцийввода-выводавыполняют дополнительнуюфункциюввода-выводаобщегоназначения. Микроконтроллеримеет встроенный IRC-генераторсточностью до ±1% впромышленных диапазонах температурина пряжений. Возможна подачатак товых импульсов свнешнегоисточника.

МикроконтроллерLPC1102поддерживаютразличныеинструментальныесредстваразработкистороннихорганизаций, а такжесобственнаяплатформаразработки—LPCXpresso,котораяимеетмощнуюинтегрированнуюсредуразработки(IDE) на базеЕсlipse, совершенноновогоинтуитивнопонятногоинтерфейса, разработанногоспециалистамикомпанииNXP, атакжекомпиляторибиблиотеки, оптимизированные подпроцессор Cortex-Mo. ОтладчикLPC-Linkиплатыдляразработки предоставляют пользователям всеинструменты, необходимые для ускорения разработки продуктов и их вывода на рынок.

Крупносерийноепроизводствоновогомикроконтроллеранамеченоначетвертыйквартал 2010года. Позднеекомпанияпланируетвыпуститьновыемикросхемымикроконтроллеров семейства LPC1100.

Дополнительнуюинформациюобэтойплатформеможно найти по адресу www.nxp.com/lpcxpresso.

# XVIII-й Международный симпозиум по передовым дисплейным технологиям 15-я Международная конференция по органической и неорганической электролюминесценции

## 27 сентября – 1 октября 2010 г. Санкт-Петербург

## Тематика конференции:

- Органические и неорганические светоизлучающие диоды

- Неорганическая электролюминесценция

- Люминофоры для дисплеев, подеветки и освещения

- Жидкие кристаллы, ЖК и трехмерные дисплеи

- Плазменные, ЭЛТ, НВКЛ и эмиссионно-полевые дисплеи.

- Электрофоретические и электрохромные дисплеи

- Микро- и проекционные дисплеи

- Дисплейная оптика, электроника и материалы

- Метрология, применения и рынок дисплеев

Представление тезисов - до 31 июня 2010

msychov@yahoo.com http://EL-10.narod.ru/