Retrascope: инструмент обратной инженерии HDL-описаний

Современные цифровые микроэлектронные системы состоят из большого числа компонентов разной сложности. Для создания таких систем активно применяются инструментальные средства поддержки. Круг задач, решаемых данными средствами, может быть достаточно широким (проверка корректности, оценка производительности и т.д.) и зависит от того, на каком этапе проектирования применяется инструмент. Процесс проектирования цифровой аппаратуры включает следующие основные этапы: 1) архитектурное проектирование, 2) детальное (логическое) проектирование, 3) синтез. Первый этап содержит составление и анализ требований, а также формирование внутренней структуры микроэлектронной системы и форматов обмена данными между отдельными компонентами. На втором этапе разрабатываются структура и потактово точное описание поведения на уровне регистровых передач (Register Transfer Level, RTL). Результатом является представление цифровой аппаратуры на одном из языков описания аппаратуры (Hardware Description Language, HDL), таких как VHDL и Verilog – HDL-описание. Синтаксис языков описания аппаратуры близок к традиционным языкам процедурного программирования, таким как C и Ada. Этап синтеза в настоящее время автоматизируется средствами современных САПР.

Сложность HDL-описаний наряду с активным использованием сторонних IP-блоков (Intellectual Property) в коммерческих проектах по разработке цифровой аппаратуры делают актуальной задачу обратной инженерии (reverse engineering) – получения сведений о принципах работы целевой системы и его внутренней структуре. На решение этой задачи нацелен расширяемый инс трумент Retrascope (Reverse Engineering and TRAnsformation) с открытым исходным кодом, разрабатываемый в ИСП РАН. Инструмент оперирует компонентами двух категорий: 1) модели – представления HDL-описаний с помощью математических формализмов; 2) обработчики – компоненты, выполняющие преобразование и анализ моделей.

В настоящее время поддерживаются следующие виды моделей, автоматически извлекаемые инструментом из исходного кода HDL-описаний:

- Граф потока управления (Control flow graph, CFG);

- Решающая диаграмма охраняемых действий (Guarded actions decision diagram, GADD);

- Высокоуровневая решающая диаграмма (High level decision diagram, HLDD);

- Расширенный конечный автомат (Extended finite state machine, EFSM).

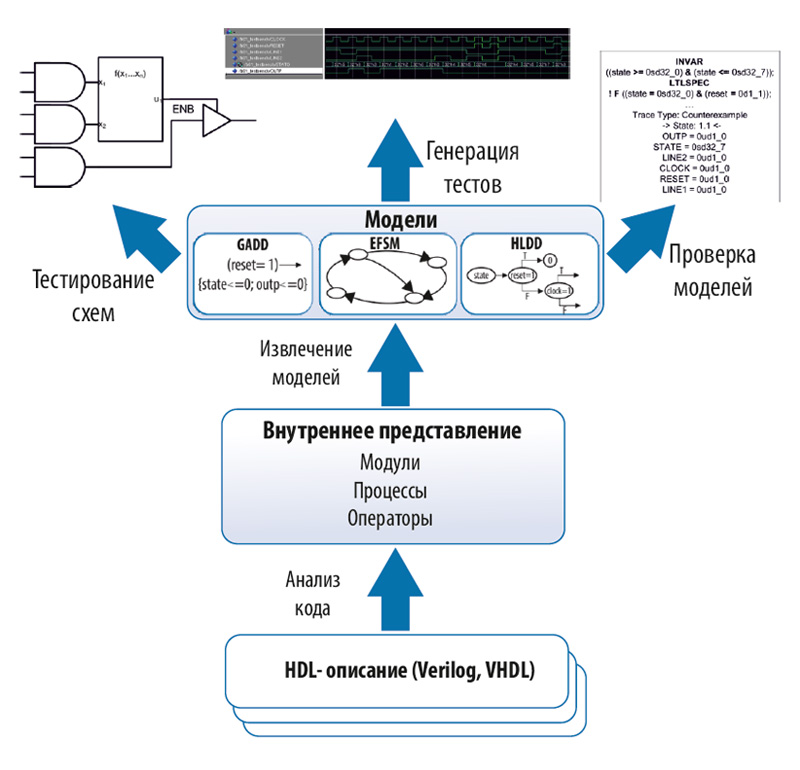

Возможные сценарии использования инструмента Retrascope представлены на Рисунке 1. На вход подается описание аппаратуры на языке VHDL или Verilog. Инструмент анализирует исходный код, результатом работы является построение внутреннего представления аппаратуры на базе графа потока управления. Внутреннее представление содержит всю информацию, представленную в исходном HDL-описании. Затем выполняется автоматическое извлечение формальных моделей. Извлеченные модели могут быть визуализированы в формате GraphML, либо с помощью надстройки (plug-in) Retrascope IDE для среды разработки Eclipse. Надстройка также позволяет запускать сам инструмент Retrascope, а также настраивать последовательности выполнения внутренних обработчиков. Использование надстройки не является обязательным – с инструментом можно работать и с помощью интерфейса командной строки.

Рисунок 1. Сценарии использования Retrascope.

Одним из вариантов последующего использования извлеченных формальных моделей является их применение к функциональной верификации – проверке функциональной корректности целевого устройства. В настоящее время для функциональной верификации применяются динамический (имитационный) и статический подходы. Под имитационной верификацией обычно понимается тестирование HDL-моделей аппаратуры, выполняемое в специальной среде имитационного моделирования — HDL-симуляторе. Статическая верификация основана на построении математической (формальной) модели системы и ее анализе на предмет выполнимости свойств, также выраженных формально (например, свойство безопасности (safety) — недостижимости ошибочных состояний, и свойство живости (liveness) — отсутствия зависаний и зацикливаний). Также существуют гибридные методы, которые используют комбинации указанных подходов. Данные методы сочетают в себе преимущества традиционных методов и не так страдают от их недостатков. Инструмент Retrascope позволяет разраба- тывать гибридные техники верификации HDL-описаний за счет комбинирования различных средств анализа формальных моделей. Результатами работы инструмента в таком случае являются тесты – последовательности значений входных сигналов, приводящие к выполнению некоторого условия. Например, на основе анализа расширенного конечного автомата (EFSM), извлеченного из исходного кода, может быть построен набор тестов, покрывающий все пути выполнения целевого устройства. В настоящее время в инструменте Retrascope реализованы генераторы тестов следующих типов:

- Генератор случайных тестов заданной длины (на основе CFG);

- Генератор тестов на основе симуляции EFSM;

- Генератор тестов на основе проверки моделей (на основе EFSM и HLDD);

Проведенные эксперименты показывают существенное сокращение общей длины сгенерированных тестов по сравнению с существующими подходами при высоком уровне покрытия кода HDL-описания.

Исполнитель

Перейти к списку всех проектов